## **USENIX** Association

# Proceedings of the 2022 USENIX Annual Technical Conference

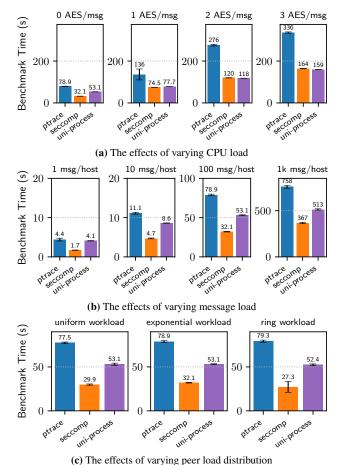

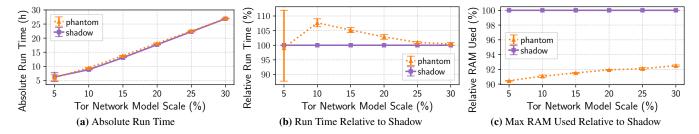

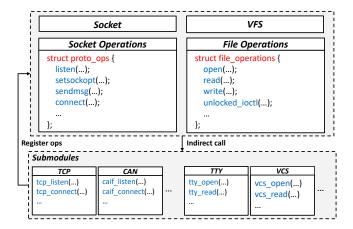

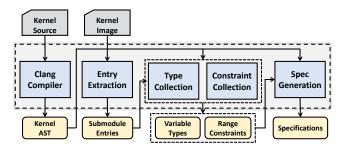

July 11–13, 2022 Carlsbad, CA, USA

#### © 2022 by The USENIX Association

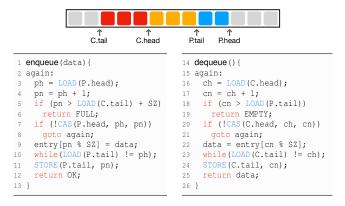

#### All Rights Reserved

This volume is published as a collective work. Rights to individual papers remain with the author or the author's employer. Permission is granted for the noncommercial reproduction of the complete work for educational or research purposes. Permission is granted to print, primarily for one person's exclusive use, a single copy of these Proceedings. USENIX acknowledges all trademarks herein.

ISBN 978-1-939133-29-8

## **Conference Organizers**

**Program Co-Chairs**

Jiri Schindler, *Tranquil Data*

Noa Zilberman, University of Oxford

**Program Committee**

Reto Achermann, University of British Columbia

Gustavo Alonso, *ETH Zurich*Raja Appuswamy, *EURECOM*Anys Bacha, *University of Michigan*Saurabh Bagchi, *Purdue University*

Yungang Bao, Institute of Computing Technology, Chinese

Academy of Sciences

${\bf Antonio\ Barbalace}, {\it University\ of\ Edinburgh}$

Yaniv Ben Itzhak, *VMware Research* Annette Bieniusa, *TU Kaiserslautern*

Roberto Bifulco, NEC Laboratories Europe

Laurent Bindschaedler, Massachusetts Institute of Technology

William Bolosky, Microsoft Research

James Bottomley, IBM Research

Nathan Bronson, Rockset

Mihai Budiu, *VMware Research* Somali Chaterji, *Purdue University*

Lydia Chen, Delft University of Technology

Young-ri Choi, UNIST (Ulsan National Institute of Science and Technology)

David Cock, ETH Zurich

Dilma Da Silva, Texas A&M University

Angela Demke Brown, University of Toronto

Fred Douglis, Peraton Labs

Abhinav Duggal, *Dell EMC*Pascal Felber, *University of Neuchatel*Pedro Fonseca, *Purdue University*Wei Gao, *University of Pittsburgh*

Eran Gilad, Yahoo Research

Yotam Harchol, DFINITY Foundation

Tim Harris, Microsoft

Niranjan Hasabnis, *Intel Labs* David Hay, *Hebrew University*

Michio Honda, University of Edinburgh

Jon Howell, VMware

Yu Hua, Huazhong University of Science and Technology

Joo-young Hwang, Samsung Electronics

Rebecca Isaacs, Twitter

Zsolt Istvan, TU Darmstadt

Anand Iyer, Microsoft Research

Bill Jannen, Williams College

Theo Jepsen, Stanford University

Anuj Kalia, *Microsoft* Michael Kozuch, *Intel Labs*

John Kubiatowicz, *University of California*, *Berkeley* Youngjin Kwon, *Korea Advanced Institute of Science and*

Technology (KAIST)

Sándor Laki, ELTE Eötvös Loránd University

Shir Landau Feibish, The Open University of Israel

Alberto Lerner, University of Fribourg

Youyou Lu, Tsinghua University

Xiaosong Ma, Qatar Computing Research Institute

Ilias Marinos, Microsoft Research

A. Theodore Markettos, University of Cambridge

Ali Mashtizadeh, University of Waterloo

Michael Mesnier, Intel

Ethan Miller, University of California, Santa Cruz / Pure Storage

Changwoo Min, Virginia Tech

Subrata Mitra, Adobe Research

Jayashree Mohan, Microsoft Research India

${\bf Sue\ Moon}, Korea\ Advanced\ Institute\ of\ Science\ and\ Technology$

(KAIST)

Kiran-Kumar Muniswamy-Reddy, Amazon

Onur Mutlu, ETH Zurich

Khanh Nguyen, Texas A&M University

Ruslan Nikolaev, The Pennsylvania State University

Shadi Noghabi, Microsoft Research

Fernando Pedone, Università della Svizzera italiana

Adrian Perrig, *ETH Zurich* Babu Pillai, *Intel Labs*

Thanumalayan Pillai, Google

Fernando Ramos, Universidade de Lisboa

Kaveh Razavi, ETH Zurich

Elissa M. Redmiles, Max Planck Institute for Software Systems

Larry Rudolph, Two Sigma Investments, LP

Russell Sears, Apple

Mark Silberstein, Technion—Israel Institute of Technology Georgios Smaragdakis, Delft University of Technology

Keith A. Smith, *MongoDB* Ripduman Sohan, *Xilinx* Patrick Stuedi, *Meta*

Nik Sultana, *Illinois Institute of Technology* Vasily Tarasov, *IBM Research - Almaden*

Alain Tchana, ENS Lyon, France Jens Teubner, TU Dortmund Eno Thereska, Amazon

Daniel Thomas, University of Strathclyde

Theodore Ts'o, Google

Shay Vargaftik, VMware Research

Nandita Vijaykumar, *University of Toronto*

Haris Volos, *University of Cyprus* Keval Vora, *Simon Fraser University*

Han Wang, Intel

Ric Wheeler, Facebook

Avani Wildani, *Emory University* Dan Williams, *Virginia Tech*

Youjip Won, Korea Advanced Institute of Science and Technology (KAIST)

Eiko Yoneki, University of Cambridge

Yibo Zhu, ByteDance

### **External Reviewers**

Amit Levy

Aravind Machiry

Calin Iorgulescu

Chia-Che Tsai Jasmina Malicevic Minjia Zhang Reza Yazdani Aminabadi Roberto Palmieri Valerio Schiavoni

## Message from the USENIX ATC '22 Program Co-Chairs

#### Introduction

Welcome to the 2022 USENIX Annual Technical Conference (ATC). We are excited that, after two years of being virtual due to the COVID-19 pandemic, this year's conference is held again in person. Because of the ongoing special circumstances, USENIX has adopted a hybrid model with some attendees and presenters connecting remotely.

Similar to last year, ATC 2022 is co-located with OSDI. Our 2021 predecessors have already written extensively about the opportunities and challenges of running two systems conferences at the same time (https://www.usenix.org/sites/default/files/atc21\_message.pdf). This year brings the new challenge of running the two co-located events in a hybrid model. We very much look forward to meeting everyone in the systems community whether they attend ATC, OSDI, or both.

The rest of this document provides some insights into the submission and selection process that culminated in 64 accepted works that will be presented at the conference.

#### **Submissions process**

We have solicited full length and short papers presenting new and original computer systems work. We adopted a double-blind review process to minimize bias. To further the USENIX mission of bringing together researchers in academia and systems practitioners, we have designated a special Operational Systems Track (OST) category to solicit submissions describing the experiences from deployed systems at "production" scale with real-world data. OST submissions received the same rigorous review process but with different criteria. The submission's novelty bar was lower, and system and organization names did not have to be blinded. Switching submission tracks after the deadline was forbidden.

Authors were requested to provide additional information with their submission. First, we asked whether the paper was a re-submission from prior ATC or some other conference. 65% of the papers were marked as first-time submissions and 45% of the accepted papers were first time submissions. In case of a resubmission, authors provided a description of what changes they made since the previous submission. The reviewers and the program committee (PC) had access to this information, but they did not know the venue where the paper was submitted or specific review comments (unless provided by the authors). Prior submission information had no bearing on assigning reviewers.

We also asked the authors to indicate whether they would make an artifact available. 70% of submissions indicated they would, if accepted. With all else being equal, the PC viewed more favorably submissions that would share an artifact over those that did not. As researchers, we need to ensure reproducibility of published works. As members of the USENIX community, we want to provide free and open access to data. The artifact evaluation process, which we instituted this year together with OSDI, provides this assurance.

We received 394 submissions, of which 21 (5%) were in OST and 23 (6%) were short papers. This was about 15% more submissions than in the previous two years. We rejected 5 submissions without a review due to violating one or more directives stated in the call for papers (CFP). The most popular submission topics were Distributed System (26%), Storage (24%), Machine Learning (21%), Operating Systems (15%), Networking (14%), Databases (13%) and Security (13%).

In the end, the PC accepted 64 submissions for an overall 16.5% acceptance rate. Acceptance was based on the quality of the submissions, while in-person conference constraints had no bearing on our decisions. Of the 64 accepted submissions, 7 (33% acceptance rate) were in Operational Systems Track and 2 (9% acceptance rate) were short papers.

### **Program Committee**

We have assembled a program committee with many goals in mind: good coverage across diverse computer systems topics, balance between academia and industry, a mix of veterans of prior ATC PCs with individuals in early stages of their professional careers, geographic diversity, and adherence to the USENIX diversity and inclusion principles.

The assembled PC had 97 members from 15 countries, 52% from North America, 37% from EMEA and 10% from APAC. 60% of the PC were from academia and 40% from industry, though some PC members from academia were also affiliated with industry. 36% of the reviewers were early career researchers. Women were 64% more likely to decline an invitation to join the PC, which we find to be an alarming indication.

The main areas of expertise of PC members were Storage (22%), Distributed Systems (20%), Operating Systems (14%), Security (13%), Networking (12%) and Databases (9%). This was a good match to the submissions topics, given the PC was assembled in advance. As only 9% of PC members indicated that Machine Learning is their main expertise, a mismatch with 21% of submissions, we expanded the PC post submission deadline with more machine learning experts and recruited the help of a few expert external reviewers.

#### **Reviewing Process**

We proceeded with two double-blind review rounds with the authors' response after round 2 and before the PC meeting. We sent early rejection notifications to 58% of papers 10 weeks after the initial submission to allow authors a quick turnaround on their resubmission. In the first round, we assigned 3 reviewers per paper, in the vast majority of cases, complementing the expertise with external reviewers as necessary. In the second round, we assigned at least two additional reviewers to the 162 submissions not rejected earlier.

After the authors' response and an online discussion among the reviewers (with some papers receiving over 20 comments), we pre-accepted 48 papers. We identified additional 39 papers for discussion at the face-to-face (virtual) PC meeting, of which 42% of papers were accepted, and PC members had the opportunity to "revive" papers. Despite having PC members spanning a geographic area of 13 time zones, we conducted the virtual meeting "live". While the day (and night) was long, with the usual logistical challenges of handling conflicts virtually in break-out rooms, we found that the ability to discuss and calibrate our acceptance criteria during the PC meeting was very important and proved very useful.

#### **Artifact Evaluation Process**

For the first time this year, ATC adopted an artifact evaluation process. The process ran jointly with OSDI, led by Anuj Kalia, Neeraja J. Yadwadkar, and Chengyu Zhang. The artifact evaluation committee chairs assembled a committee consisting of 118 members.

The authors of all accepted papers were invited to submit an artifact for an evaluation. 52 out of 64 papers (81%) had done so. 88% of artifacts received an "Available" badge, 76% received a "Functional" badge, and 61% received a "Reproduced" badge. 51% of papers received all three badges (some artifacts were reproduced, but are not available). Only one artifact received no badge.

#### **Additional Observations**

Strong papers easily stood out; 38% of the accepted papers received only positive reviews, and an additional 44% had only a single weak-reject initial recommendation. This is also why so many papers were accepted prior to the PC discussion.

The Operational System Track (OST) was intended only for operational systems, especially those deployed at scale. In particular, there was an interest in the experience using these operational systems. Some authors mistook a working prototype for an operational system. While all submissions to ATC are expected to describe working systems, a prototype implementation to gather experimental results is not the same. OST submissions required describing the experience of using the system.

Anonymization rules were not always followed. Only one paper was rejected immediately during post-submission checks for deblinding authors names and affiliations. However, several papers were rejected following the first round of reviews, as authors had a technical report using a similar title or a similar system name. This, in turn, led to unblinding the papers to reviewers and violated the submission rules. Anonymization rules, especially when applied to technical reports, vary from year to year and between conferences. Authors should be extra vigilant when submitting blinded manuscripts.

### Acknowledgements

More than 200 people have contributed to the organization of the USENIX ATC '22, most of them in a voluntary capacity. We would like to thank each and every one of them. We are tremendously grateful to the program committee members for a job extremely well done, and for their personal sacrifices. We thank the Artifact Evaluation committee and the Artifact Evaluation Committee Chairs for their work and contribution, which improves our community and enables future research. Last, we thank the USENIX organization, the USENIX ATC steering committee and OSDI '22 co-chairs. The amount of work and preparation that goes into organizing a conference is immense, and we were astounded by the help and support provided by everyone involved.

USENIX ATC '22 Program Co-Chairs Noa Zilberman, *University of Oxford* Jiri Schindler, *Tranquil Data*

## 2022 USENIX Annual Technical Conference July 11–13, 2022

## Monday, July 11

| Storage 1  ZNSwap: un-Block your Swap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Building a High-performance Fine-grained Deduplication Framework for Backup Storage with High Deduplication Ratio                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Secure and Lightweight Deduplicated Storage via Shielded Deduplication-Before-Encryption                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

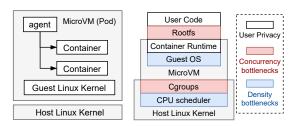

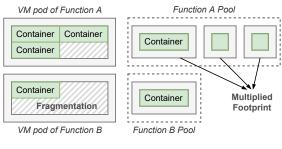

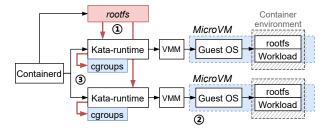

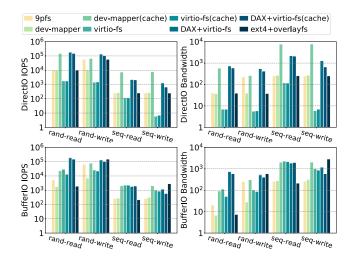

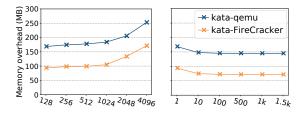

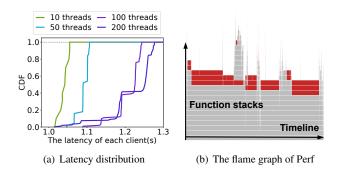

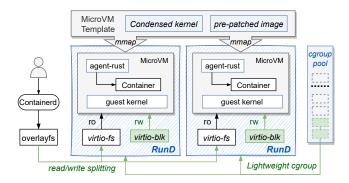

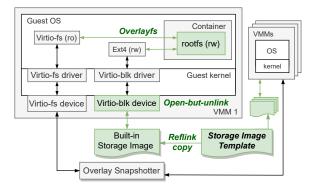

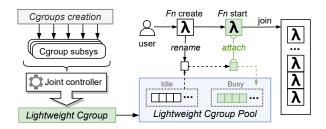

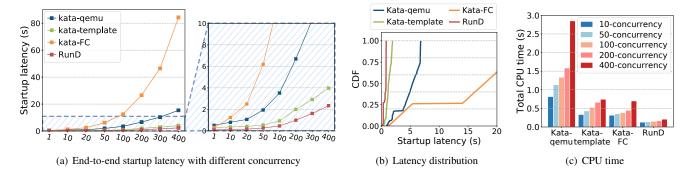

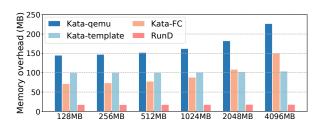

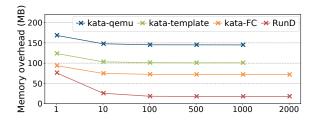

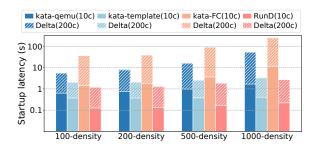

| Containers  RunD: A Lightweight Secure Container Runtime for High-density Deployment and  High-concurrency Startup in Serverless Computing.  53  Zijun Li, Department of Computer Science and Engineering, Shanghai Jiao Tong University and Alibaba Group; Jiagan Cheng, and Quan Chen, Department of Computer Science and Engineering, Shanghai Jiao Tong University; Eryu Guan, Zizheng Bian, Yi Tao, Bin Zha, Qiang Wang, and Weidong Han, Alibaba Group; Minyi Guo, Department of Computer Science and Engineering, Shanghai Jiao Tong University |

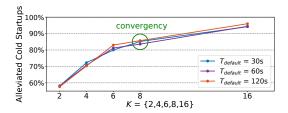

| Help Rather Than Recycle: Alleviating Cold Startup in Serverless Computing Through Inter-Function Container Sharing                                                                                                                                                                                                                                                                                                                                                                                                                                    |

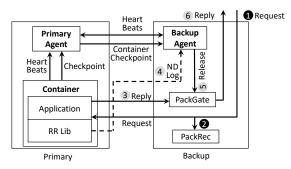

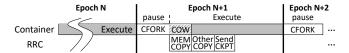

| RRC: Responsive Replicated Containers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Distributed Systems 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

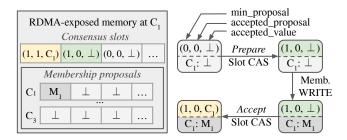

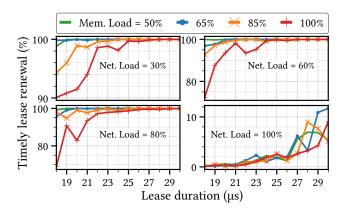

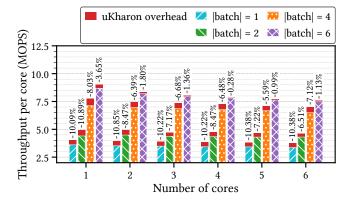

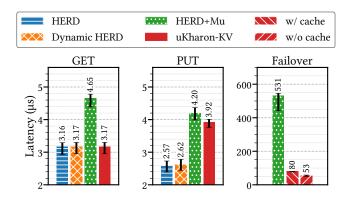

| <b>uKharon:</b> A Membership Service for Microsecond Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

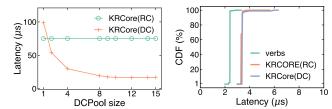

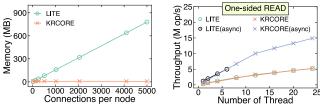

| KRCORE: A Microsecond-scale RDMA Control Plane for Elastic Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

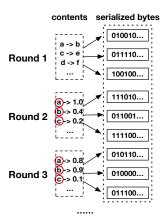

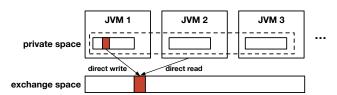

| Zero-Change Object Transmission for Distributed Big Data Analytics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Sift: Using Refinement-guided Automation to Verify Complex Distributed Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Machine Learning 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

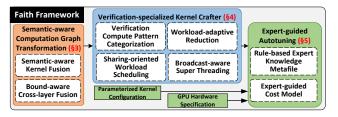

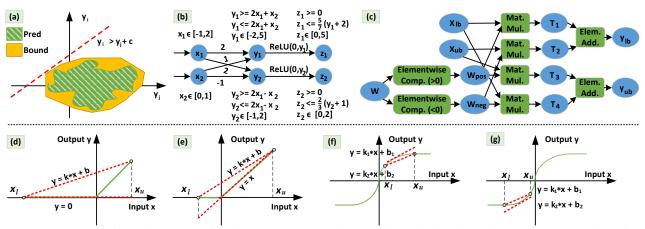

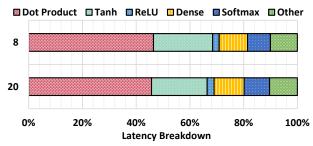

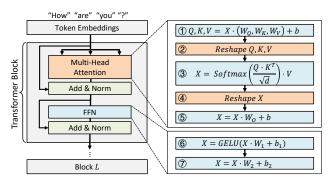

| Faith: An Efficient Framework for Transformer Verification on GPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

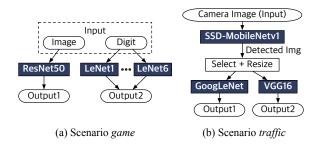

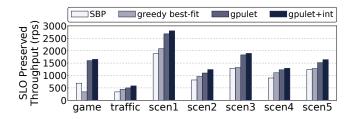

| <b>DVABatch: Diversity-aware Multi-Entry Multi-Exit Batching for Efficient Processing of DNN Services on GPUs. 183</b> Weihao Cui, Han Zhao, Quan Chen, Hao Wei, and Zirui Li, <i>Shanghai Jiao Tong University;</i> Deze Zeng, <i>China University of Geosciences;</i> Chao Li and Minyi Guo, <i>Shanghai Jiao Tong University</i> |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

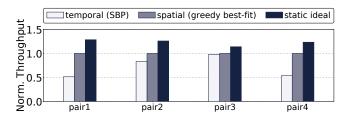

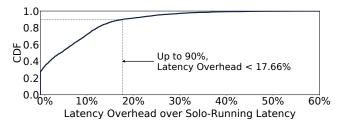

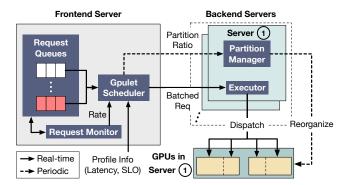

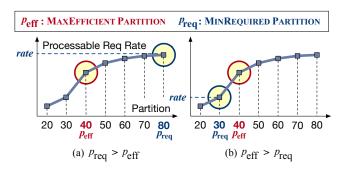

| <b>Serving Heterogeneous Machine Learning Models on Multi-GPU Servers with Spatio-Temporal Sharing 199</b> Seungbeom Choi, Sunho Lee, Yeonjae Kim, Jongse Park, Youngjin Kwon, and Jaehyuk Huh, <i>KAIST</i>                                                                                                                        |

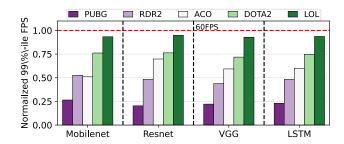

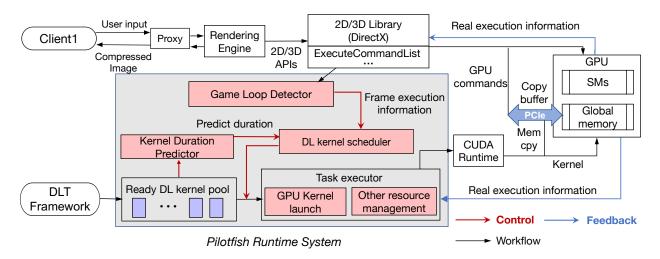

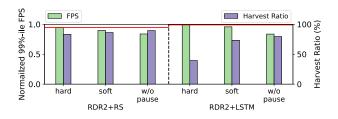

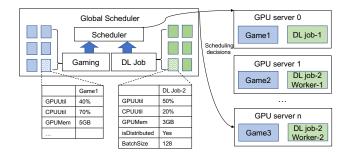

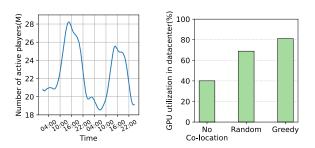

| PilotFish: Harvesting Free Cycles of Cloud Gaming with Deep Learning Training                                                                                                                                                                                                                                                       |

| Operating Systems 1                                                                                                                                                                                                                                                                                                                 |

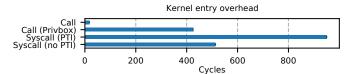

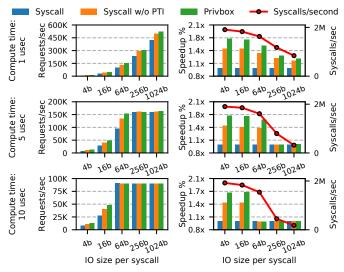

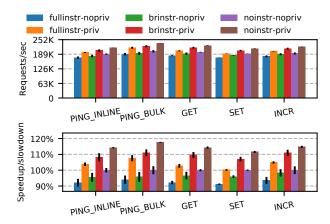

| Privbox: Faster System Calls Through Sandboxed Privileged Execution                                                                                                                                                                                                                                                                 |

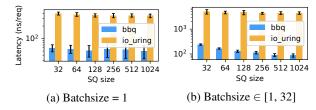

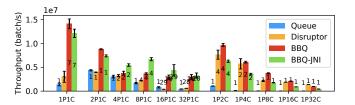

| BBQ: A Block-based Bounded Queue for Exchanging Data and Profiling                                                                                                                                                                                                                                                                  |

| Disaggregated Systems                                                                                                                                                                                                                                                                                                               |

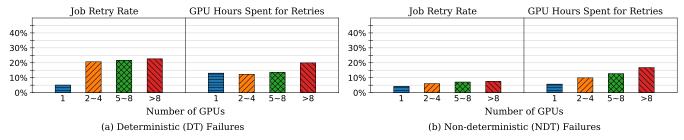

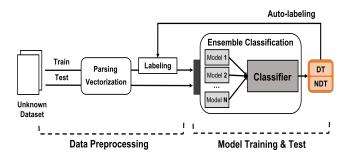

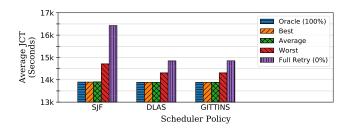

| Sibylla: To Retry or Not To Retry on Deep Learning Job Failure                                                                                                                                                                                                                                                                      |

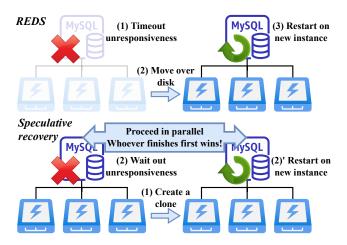

| Speculative Recovery: Cheap, Highly Available Fault Tolerance with Disaggregated Storage                                                                                                                                                                                                                                            |

| Direct Access, High-Performance Memory Disaggregation with DirectCXL                                                                                                                                                                                                                                                                |

| Networking 1                                                                                                                                                                                                                                                                                                                        |

| Not that Simple: Email Delivery in the 21st Century                                                                                                                                                                                                                                                                                 |

| AddrMiner: A Comprehensive Global Active IPv6 Address Discovery System                                                                                                                                                                                                                                                              |

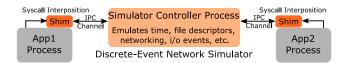

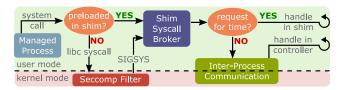

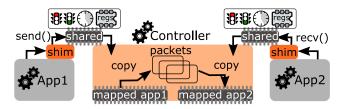

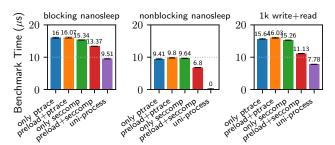

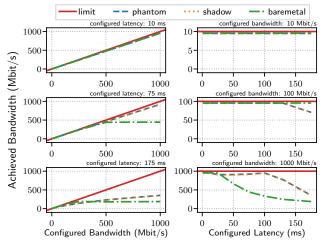

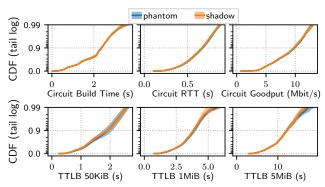

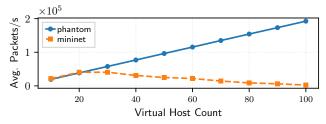

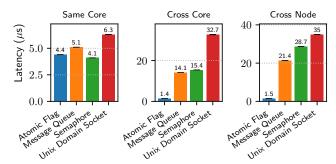

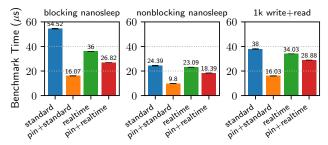

| Co-opting Linux Processes for High-Performance Network Simulation                                                                                                                                                                                                                                                                   |

| Finding Bugs                                                                                                                                                                                                                                                                                                                        |

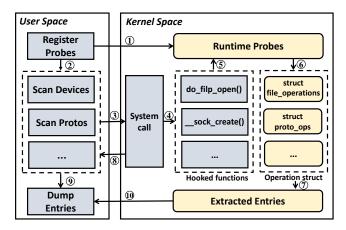

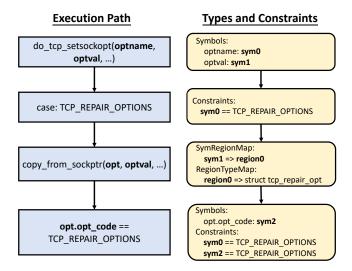

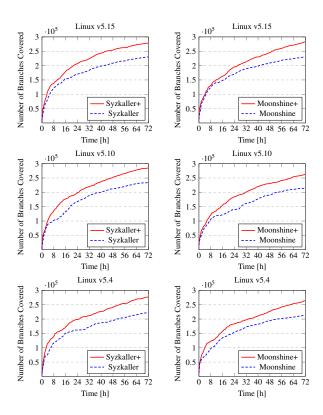

| KSG: Augmenting Kernel Fuzzing with System Call Specification Generation                                                                                                                                                                                                                                                            |

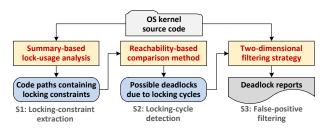

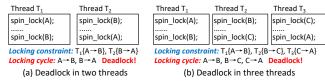

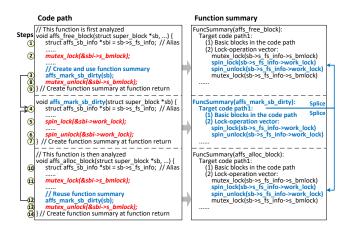

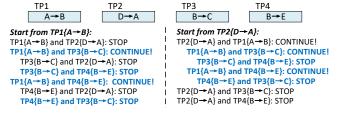

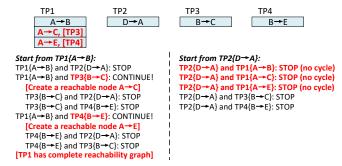

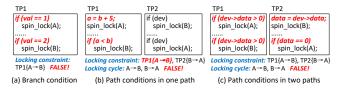

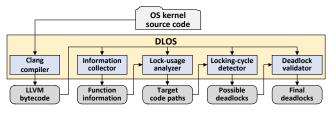

| DLOS: Effective Static Detection of Deadlocks in OS Kernels                                                                                                                                                                                                                                                                         |

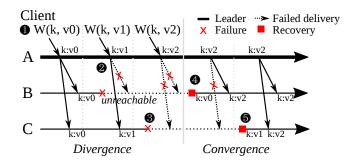

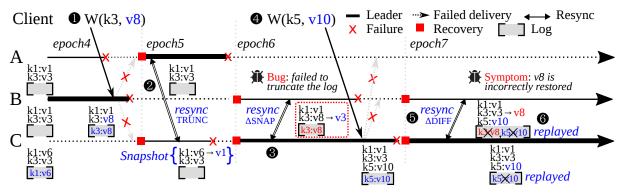

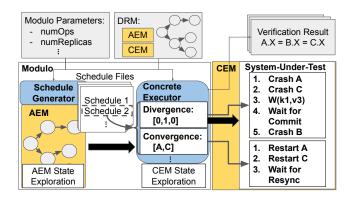

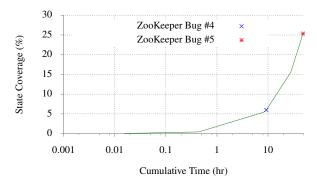

| Modulo: Finding Convergence Failure Bugs in Distributed Systems with Divergence Resync                                                                                                                                                                                                                                              |

| Models                                                                                                                                                                                                                                                                                                                              |

## Tuesday, July 12

## Security

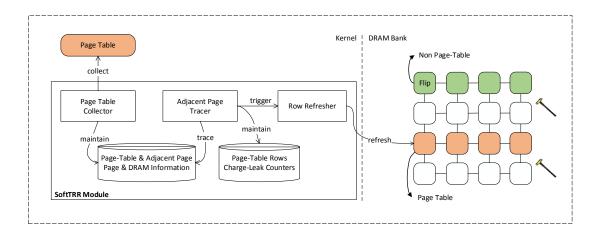

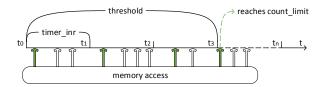

| SoftTRR: Protect Page Tables Against Rowhammer Attacks Using Software-Only Target Row Refresh                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

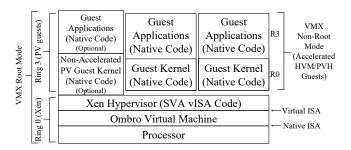

| Hardening Hypervisors with Ombro                                                                                                                                     |

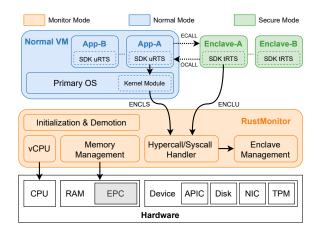

| HyperEnclave: An Open and Cross-platform Trusted Execution Environment                                                                                               |

| PRIDWEN: Universally Hardening SGX Programs via Load-Time Synthesis                                                                                                  |

| Machine Learning 2                                                                                                                                                   |

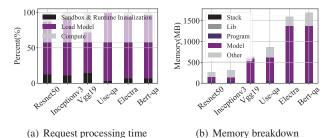

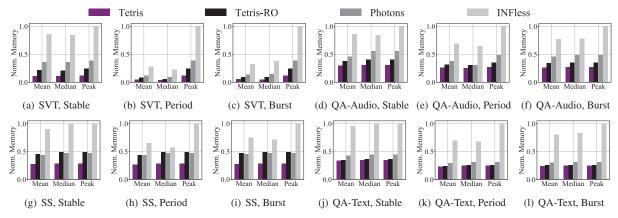

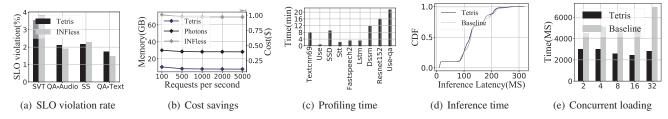

| Tetris: Memory-efficient Serverless Inference through Tensor Sharing                                                                                                 |

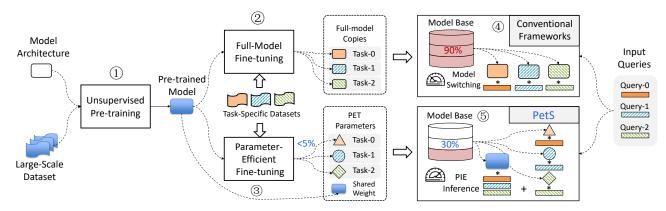

| PetS: A Unified Framework for Parameter-Efficient Transformers Serving                                                                                               |

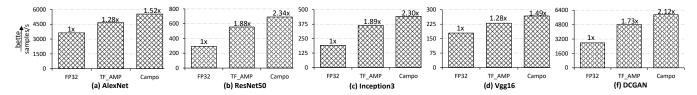

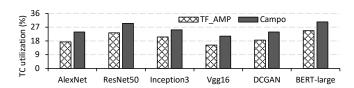

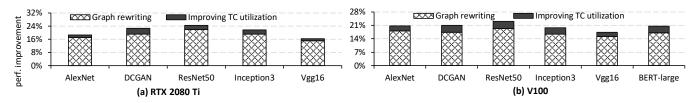

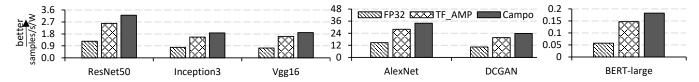

| Campo: Cost-Aware Performance Optimization for Mixed-Precision Neural Network Training                                                                               |

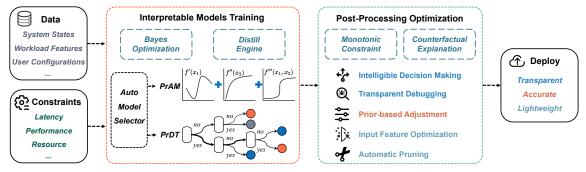

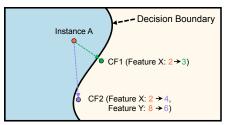

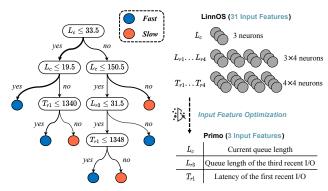

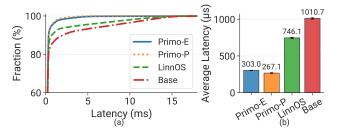

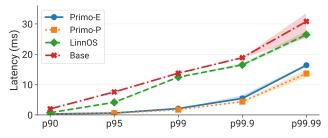

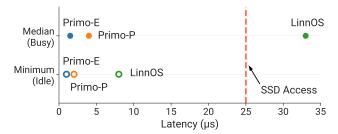

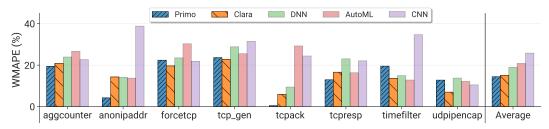

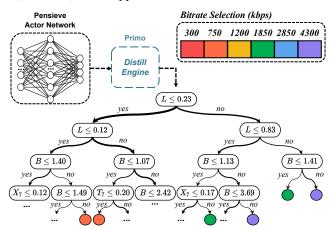

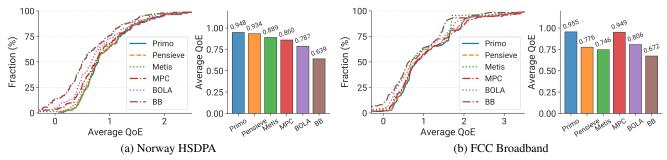

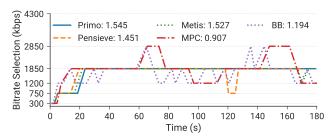

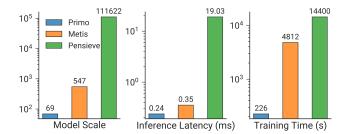

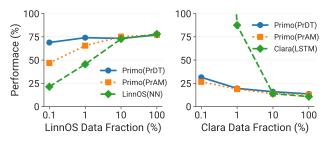

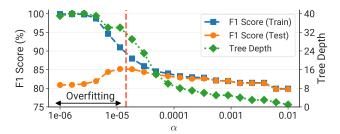

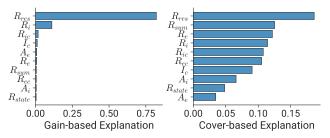

| Primo: Practical Learning-Augmented Systems with Interpretable Models                                                                                                |

| Distributed Systems 2                                                                                                                                                |

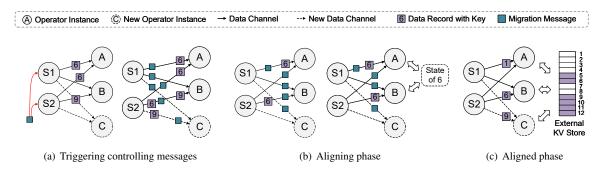

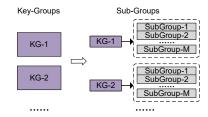

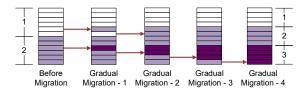

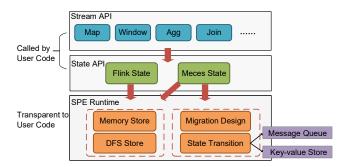

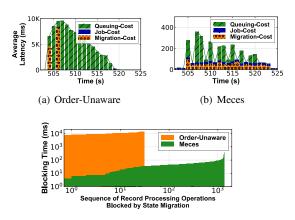

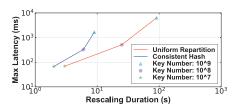

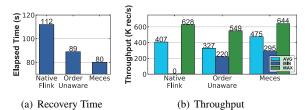

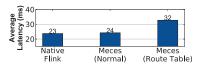

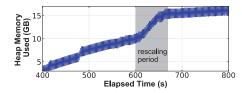

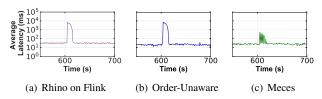

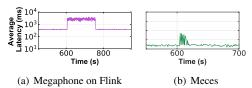

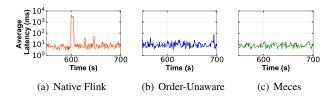

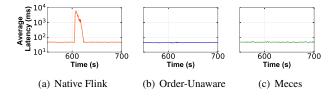

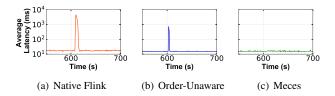

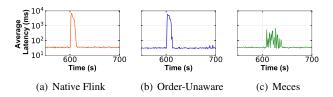

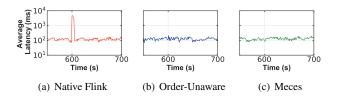

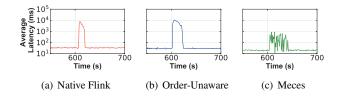

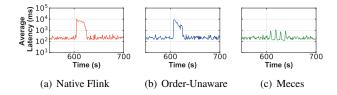

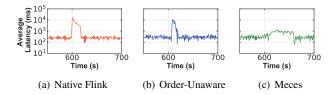

| Meces: Latency-efficient Rescaling via Prioritized State Migration for Stateful Distributed Stream                                                                   |

| Processing Systems                                                                                                                                                   |

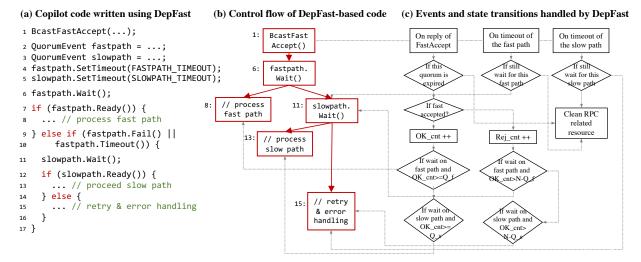

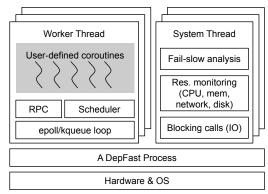

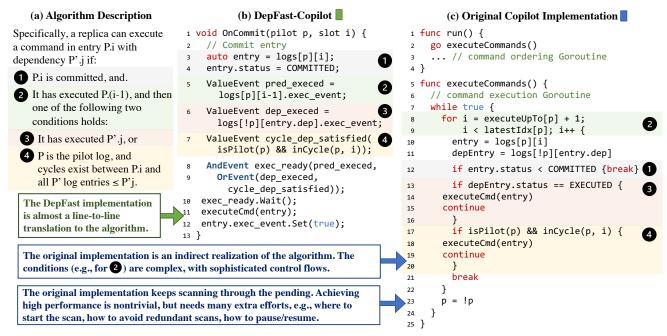

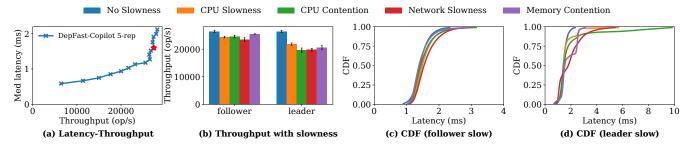

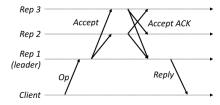

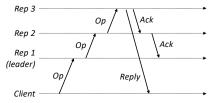

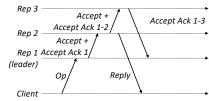

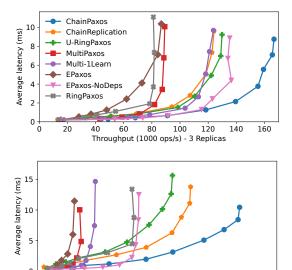

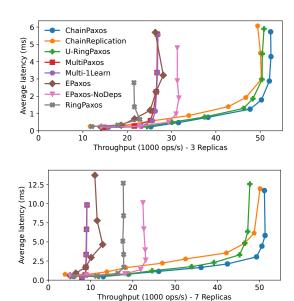

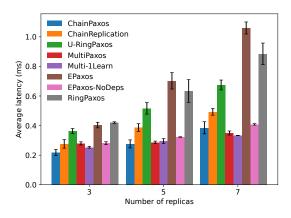

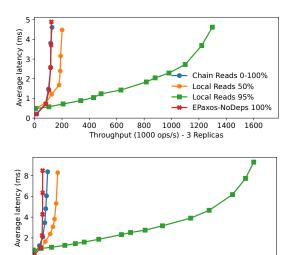

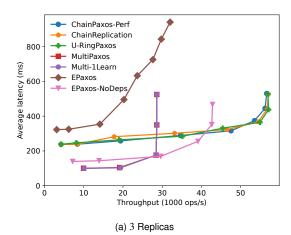

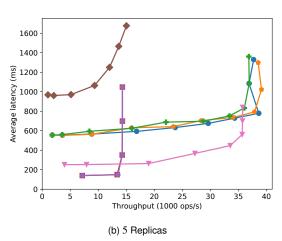

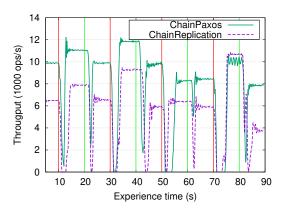

| <b>DepFast: Orchestrating Code of Quorum Systems</b>                                                                                                                 |

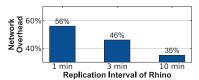

| High Throughput Replication with Integrated Membership Management       575         Pedro Fouto, Nuno Preguiça, and João Leitão, NOVA LINCS & NOVA University Lisbon |

| Operating Systems 2                                                                                                                                                  |

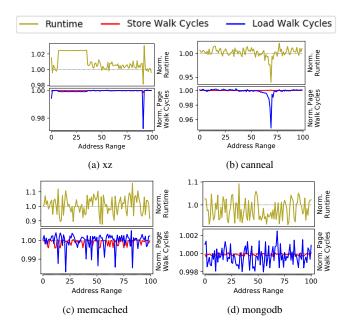

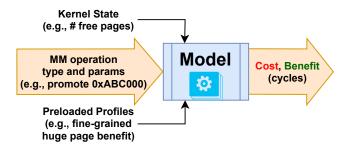

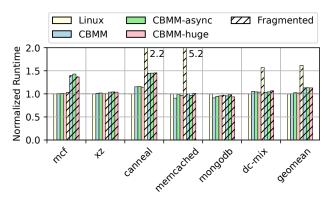

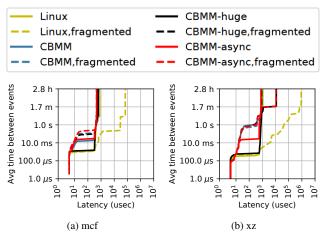

| CBMM: Financial Advice for Kernel Memory Managers                                                                                                                    |

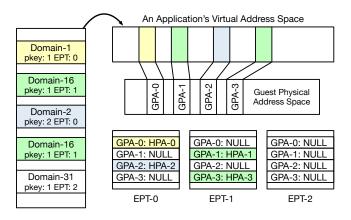

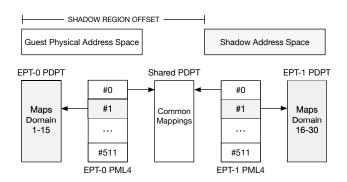

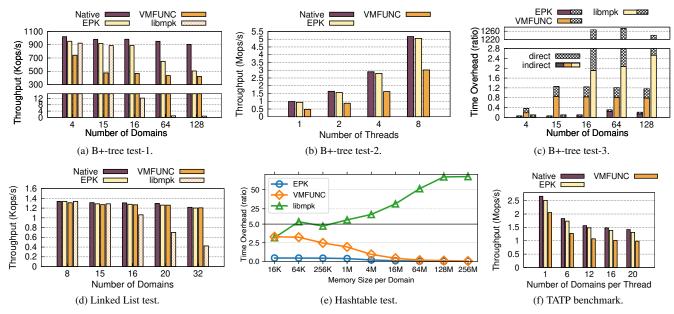

| EPK: Scalable and Efficient Memory Protection Keys                                                                                                                   |

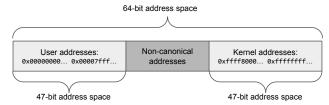

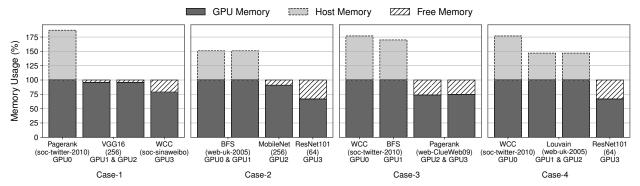

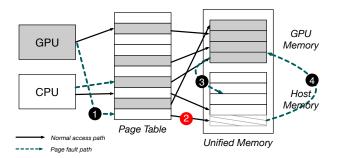

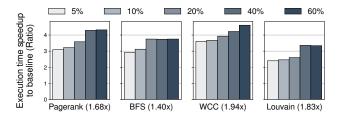

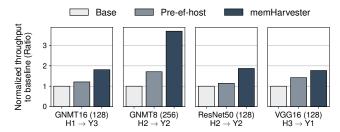

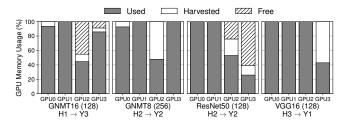

| Memory Harvesting in Multi-GPU Systems with Hierarchical Unified Virtual Memory                                                                                                                                                                                                                                                                                                                                        |   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|

| Deployed Systems 1                                                                                                                                                                                                                                                                                                                                                                                                     |   |  |  |  |  |

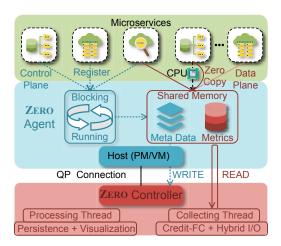

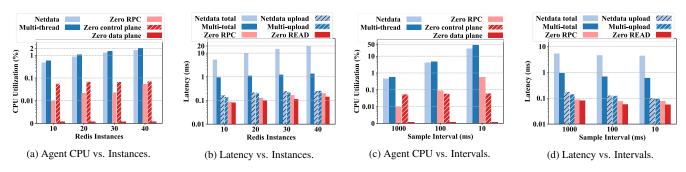

| Zero Overhead Monitoring for Cloud-native Infrastructure using RDMA                                                                                                                                                                                                                                                                                                                                                    | • |  |  |  |  |

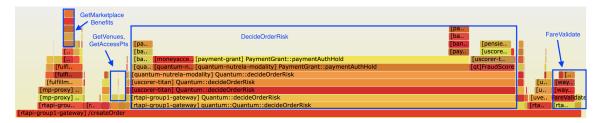

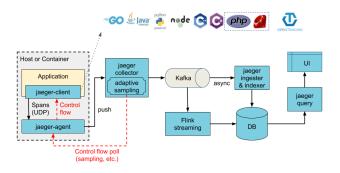

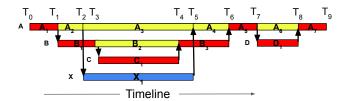

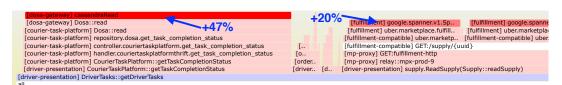

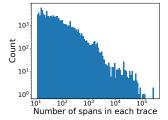

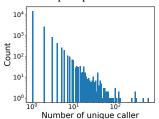

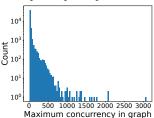

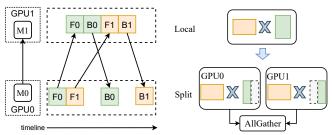

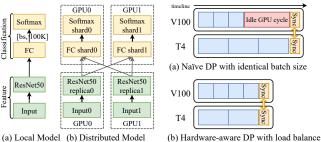

| CRISP: Critical Path Analysis of Large-Scale Microservice Architectures                                                                                                                                                                                                                                                                                                                                                | 5 |  |  |  |  |

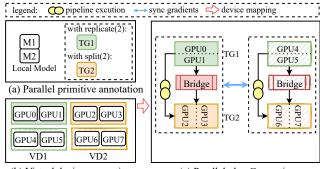

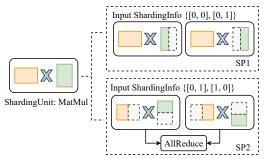

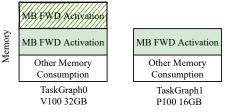

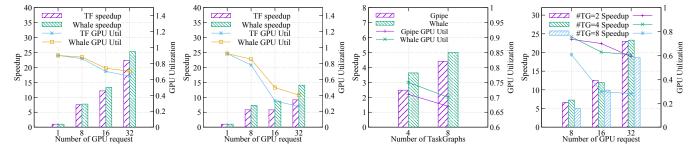

| Whale: Efficient Giant Model Training over Heterogeneous GPUs                                                                                                                                                                                                                                                                                                                                                          | 3 |  |  |  |  |

| Machine Learning 3                                                                                                                                                                                                                                                                                                                                                                                                     |   |  |  |  |  |

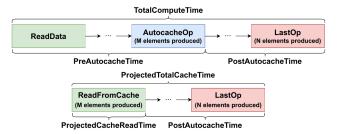

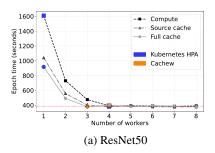

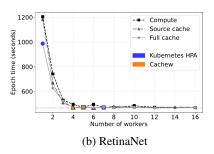

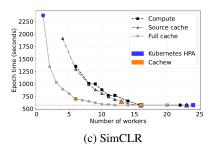

| Cachew: Machine Learning Input Data Processing as a Service                                                                                                                                                                                                                                                                                                                                                            | • |  |  |  |  |

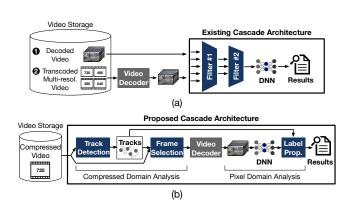

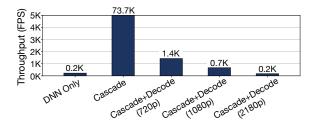

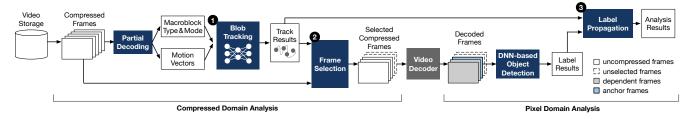

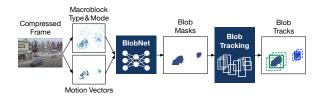

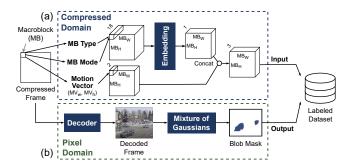

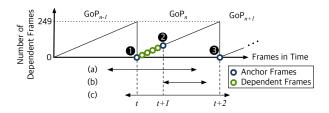

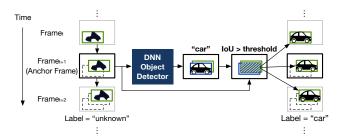

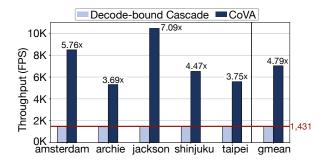

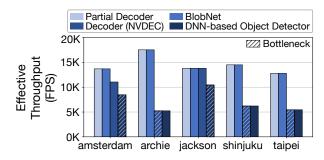

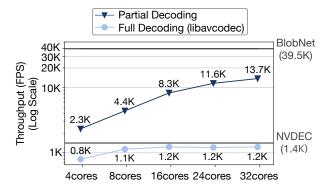

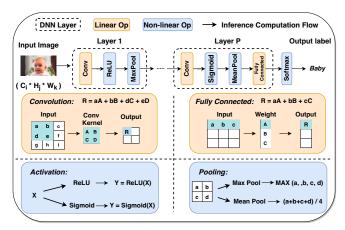

| CoVA: Exploiting Compressed-Domain Analysis to Accelerate Video Analytics                                                                                                                                                                                                                                                                                                                                              | 7 |  |  |  |  |

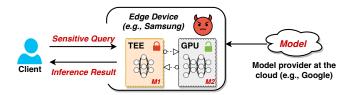

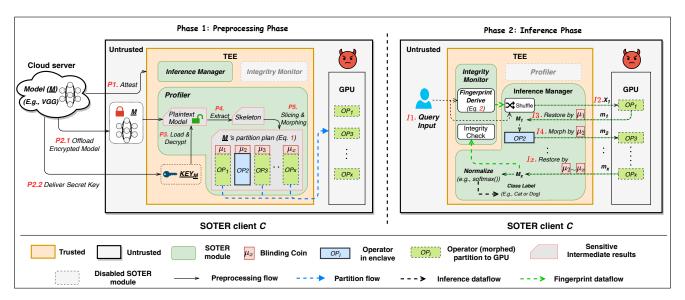

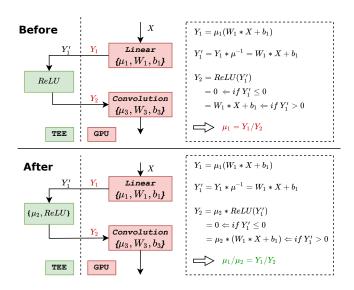

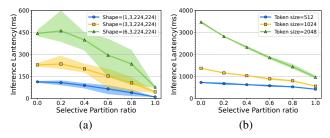

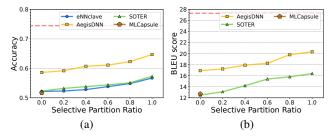

| Soter: Guarding Black-box Inference for General Neural Networks at the Edge. 723 Tianxiang Shen, Ji Qi, Jianyu Jiang, Xian Wang, Siyuan Wen, Xusheng Chen, and Shixiong Zhao, The University of Hong Kong; Sen Wang and Li Chen, Huawei Technologies; Xiapu Luo, The Hong Kong Polytechnic University; Fengwei Zhang, Southern University of Science and Technology (SUSTech); Heming Cui, The University of Hong Kong | 3 |  |  |  |  |

| Storage 2                                                                                                                                                                                                                                                                                                                                                                                                              |   |  |  |  |  |

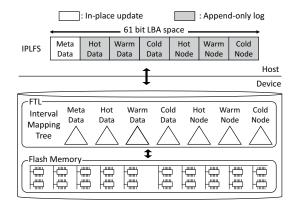

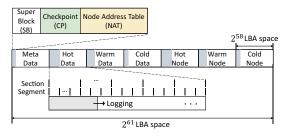

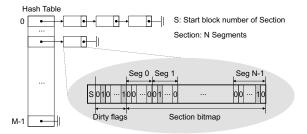

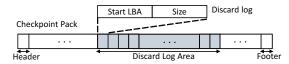

| IPLFS: Log-Structured File System without Garbage Collection                                                                                                                                                                                                                                                                                                                                                           | ) |  |  |  |  |

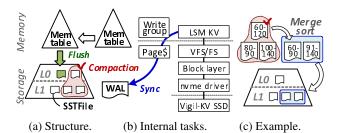

| Vigil-KV: Hardware-Software Co-Design to Integrate Strong Latency Determinism into Log-Structured Merge                                                                                                                                                                                                                                                                                                                | _ |  |  |  |  |

| Key-Value Stores                                                                                                                                                                                                                                                                                                                                                                                                       | 5 |  |  |  |  |

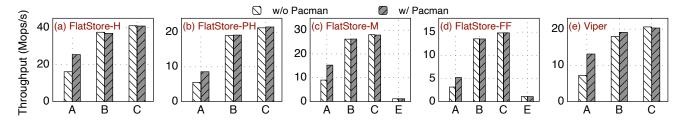

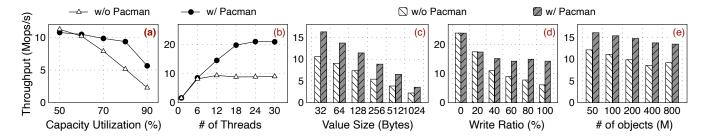

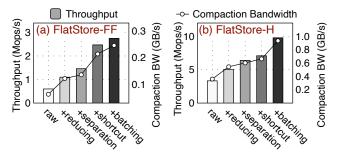

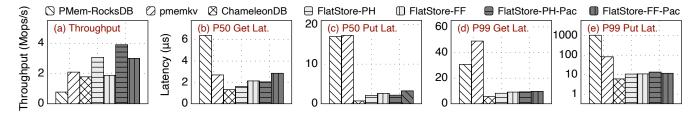

| Pacman: An Efficient Compaction Approach for Log-Structured Key-Value Store on Persistent Memory 773 Jing Wang, Youyou Lu, Qing Wang, and Minhui Xie, Tsinghua University; Keji Huang, Huawei Technologies Co., Ltd; Jiwu Shu, Tsinghua University                                                                                                                                                                     | 3 |  |  |  |  |

| Networking 2                                                                                                                                                                                                                                                                                                                                                                                                           |   |  |  |  |  |

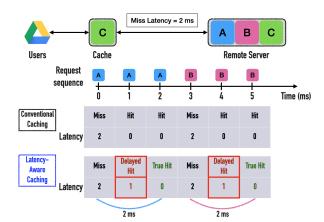

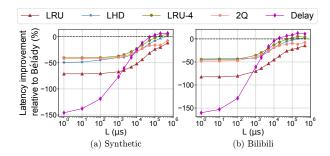

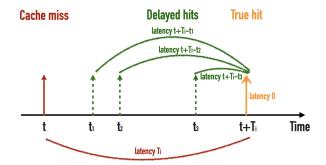

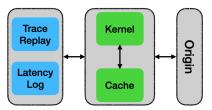

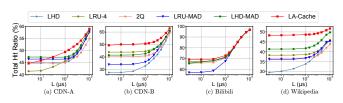

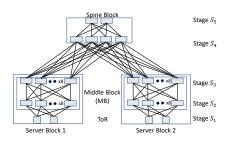

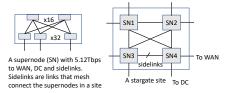

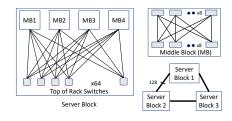

| Towards Latency Awareness for Content Delivery Network Caching                                                                                                                                                                                                                                                                                                                                                         | ) |  |  |  |  |

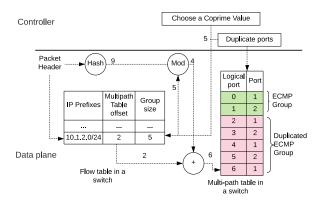

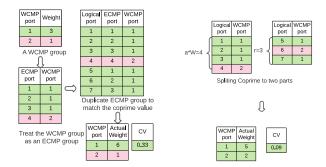

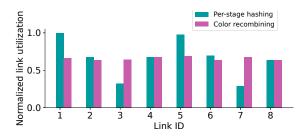

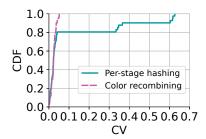

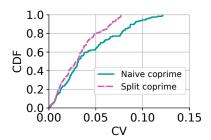

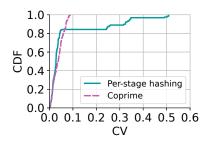

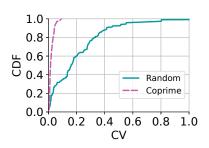

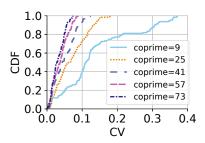

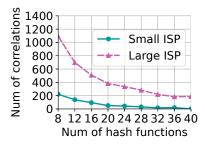

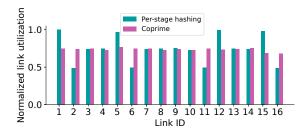

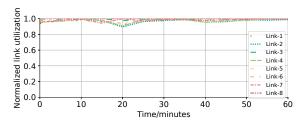

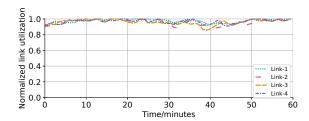

| Hashing Design in Modern Networks: Challenges and Mitigation Techniques                                                                                                                                                                                                                                                                                                                                                | 5 |  |  |  |  |

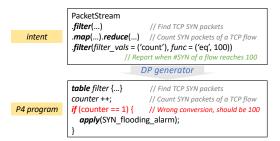

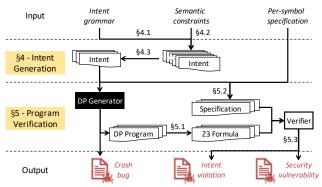

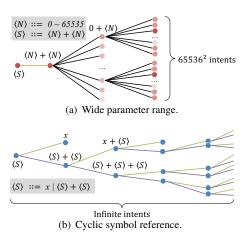

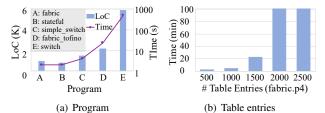

| Firebolt: Finding Bugs in Programmable Data Plane Generators                                                                                                                                                                                                                                                                                                                                                           | ) |  |  |  |  |

| Wednesday, July 13                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------|

| Compilers and PL                                                                                                                             |

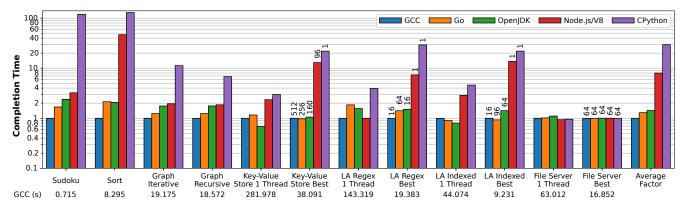

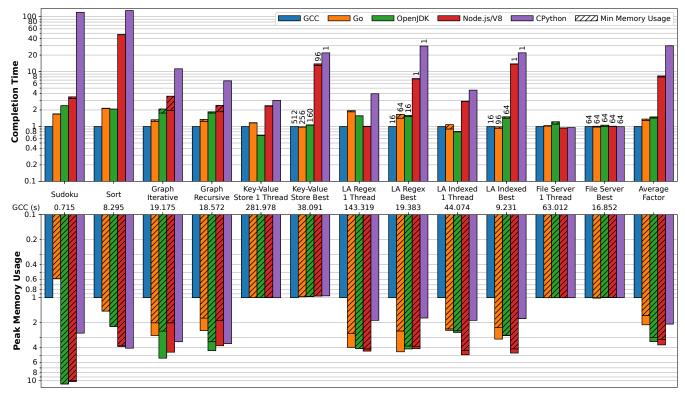

| Investigating Managed Language Runtime Performance: Why JavaScript and Python are 8x and 29x slower than C++, yet Java and Go can be Faster? |

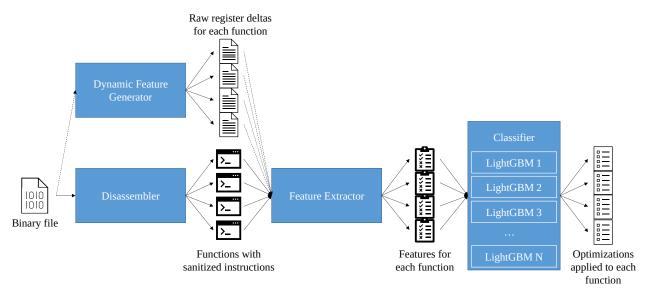

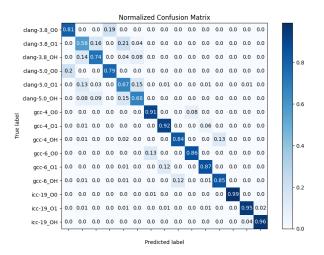

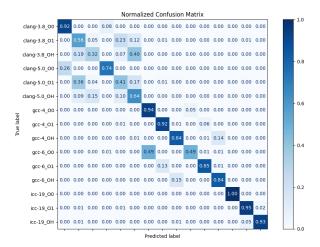

| Automatic Recovery of Fine-grained Compiler Artifacts at the Binary Level                                                                    |

| JITServer: Disaggregated Caching JIT Compiler for the JVM in the Cloud                                                                       |

| Riker: Always-Correct and Fast Incremental Builds from Simple Specifications                                                                 |

| Storage 3  FlatFS: Flatten Hierarchical File System Namespace on Non-volatile Memories                                                       |

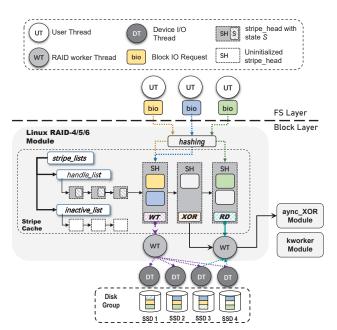

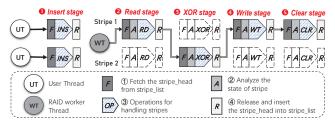

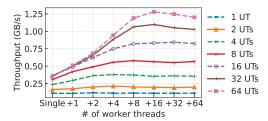

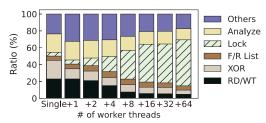

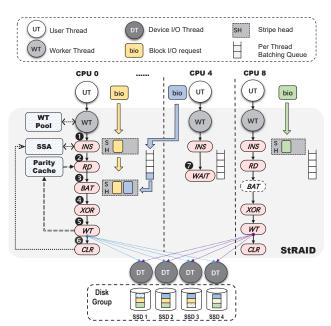

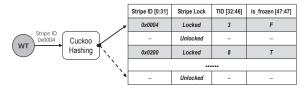

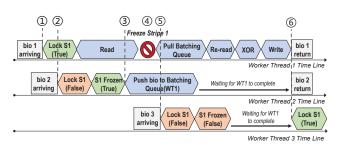

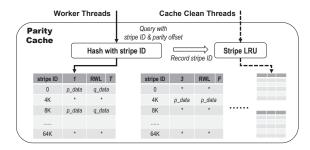

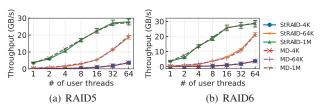

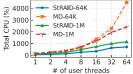

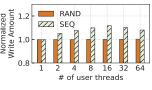

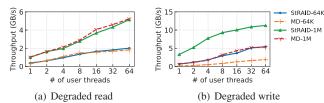

| StRAID: Stripe-threaded Architecture for Parity-based RAIDs with Ultra-fast SSDs                                                             |

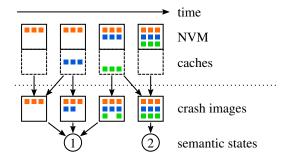

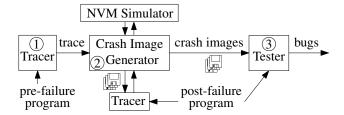

| VINTER: Automatic Non-Volatile Memory Crash Consistency Testing for Full Systems                                                             |

| NICs                                                                                                                                         |

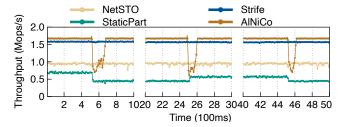

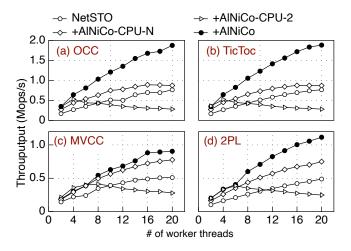

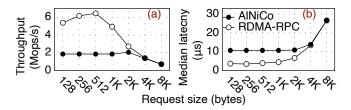

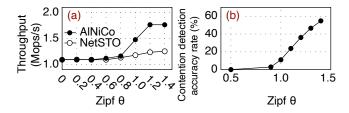

| AlNiCo: SmartNIC-accelerated Contention-aware Request Scheduling for Transaction Processing                                                  |

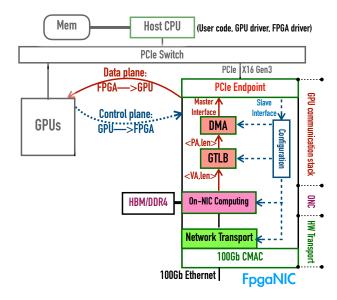

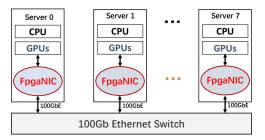

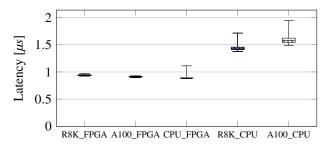

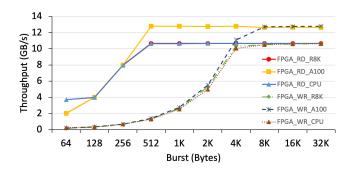

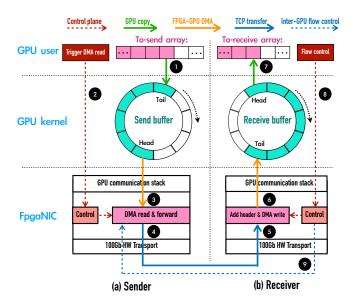

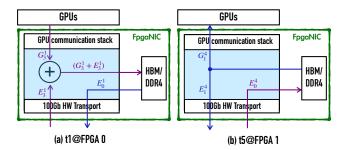

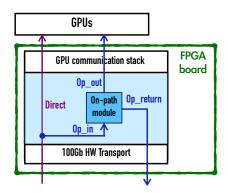

| <b>FpgaNIC:</b> An FPGA-based Versatile 100Gb SmartNIC for GPUs                                                                              |

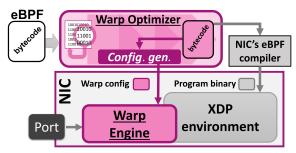

| Faster Software Packet Processing on FPGA NICs with eBPF Program Warping                                                                     |

| Deployed Systems 2                                                                                                                           |

| NVMe SSD Failures in the Field: the Fail-Stop and the Fail-Slow                                                                              |

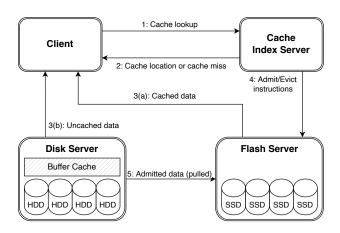

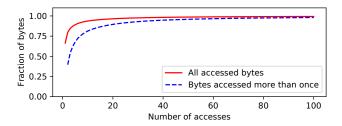

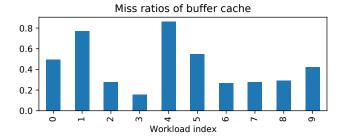

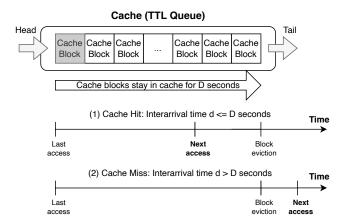

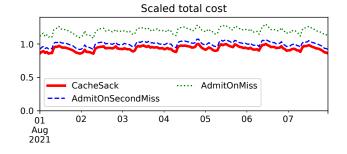

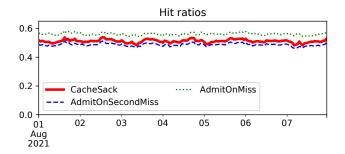

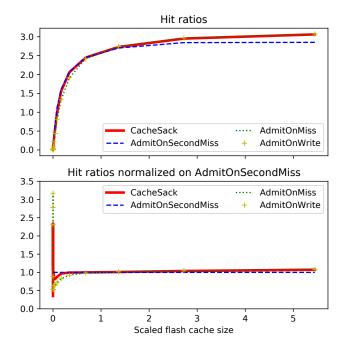

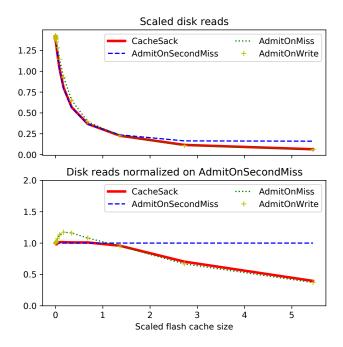

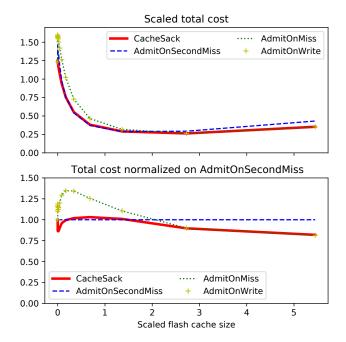

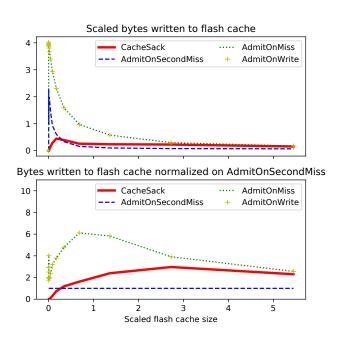

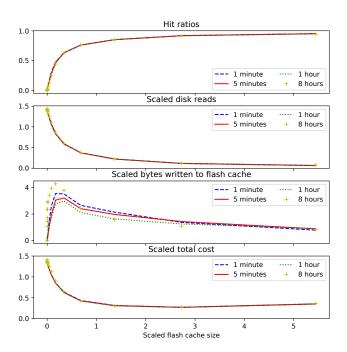

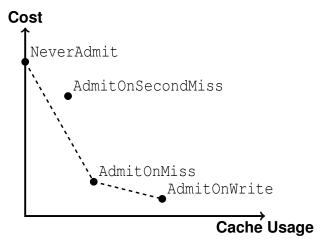

| CacheSack: Admission Optimization for Google Datacenter Flash Caches                                                                         |

| Amazon DynamoDB: A Scalable, Predictably Performant, and Fully Managed NoSQL Database Service 1037                                           |

Mostafa Elhemali, Niall Gallagher, Nicholas Gordon, Joseph Idziorek, Richard Krog, Colin Lazier, Erben Mo, Akhilesh Mritunjai, Somu Perianayagam ,Tim Rath, Swami Sivasubramanian, James Christopher Sorenson III, Sroaj Sosothikul,

Doug Terry, Akshat Vig, Amazon Web Services

#### ZNSwap: un-Block your Swap

Shai Bergman *Technion*

Niklas Cassel Western Digital Matias Bjørling Western Digital Mark Silberstein *Technion*

#### **Abstract**

We introduce ZNSwap, a novel swap subsystem optimized for the recent Zoned Namespace (ZNS) SSDs. ZNSwap leverages ZNS's explicit control over data management on the drive and introduces a space-efficient host-side Garbage Collector (GC) for swap storage co-designed with the OS swap logic. ZNSwap enables cross-layer optimizations, such as direct access to the in-kernel swap usage statistics by the GC to enable fine-grain swap storage management, and correct accounting of the GC bandwidth usage in the OS resource isolation mechanisms to improve performance isolation in multi-tenant environments. We evaluate ZNSwap using standard Linux swap benchmarks and two production key-value stores. ZNSwap shows significant performance benefits over the Linux swap on traditional SSDs, such as stable throughput for different memory access patterns, and 10× lower 99th percentile latency and 5× higher throughput for memcached key-value store under realistic usage scenarios.

#### 1 Introduction

Swap is regaining interest from the academia, industry, and kernel communities [2, 3, 12–14, 42, 43, 53, 54] as SSDs are getting faster with both low-latency NAND and high-speed PCIe interfaces [5, 11, 51]. Swap on SSDs is no longer viewed as a last-resort memory-overflow mechanism, but as a crucial system component essential for effective memory reclamation and high system efficiency [3, 14, 18].

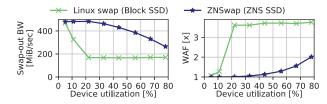

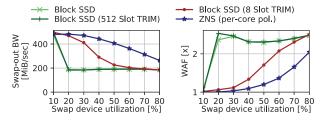

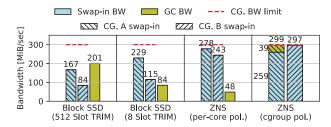

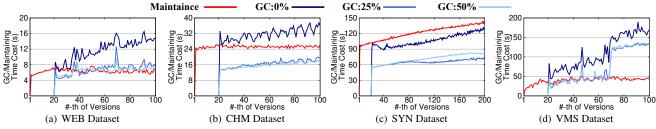

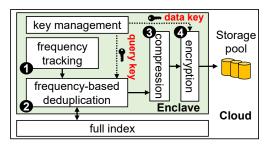

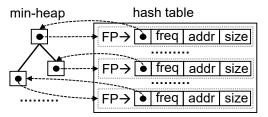

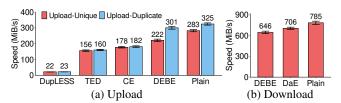

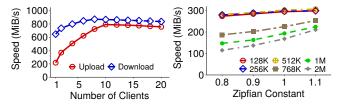

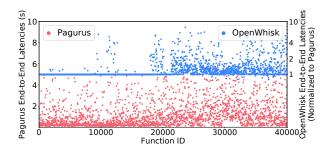

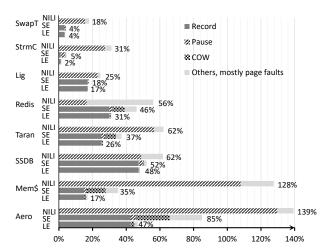

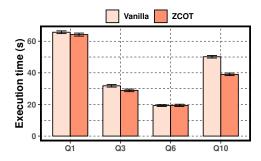

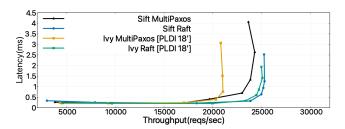

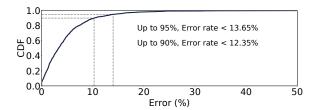

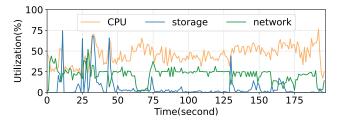

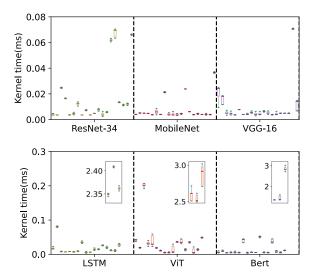

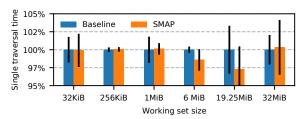

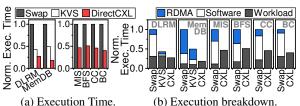

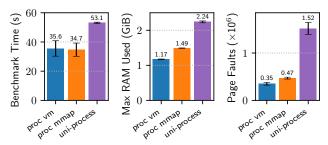

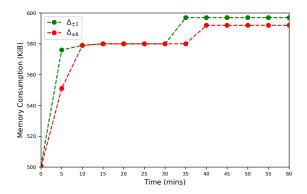

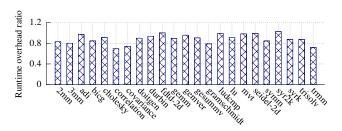

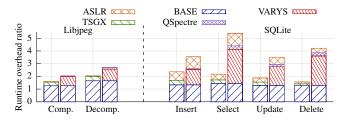

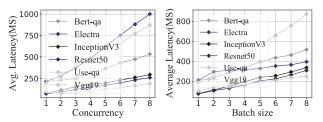

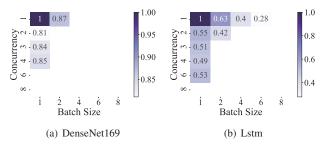

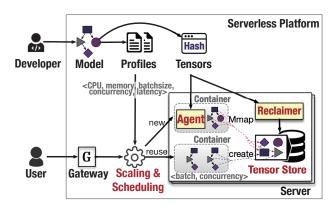

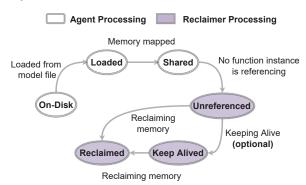

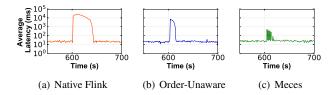

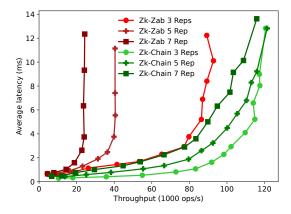

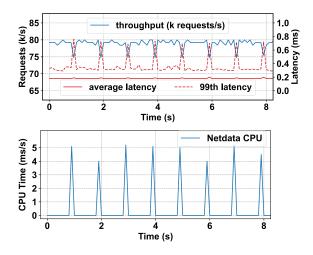

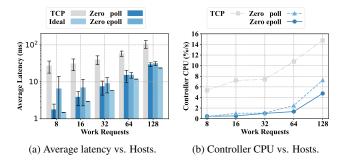

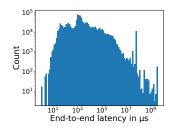

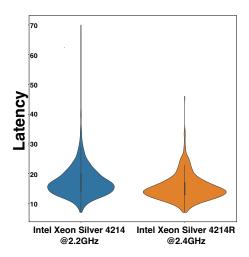

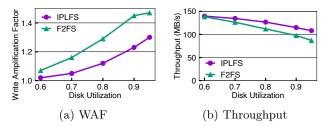

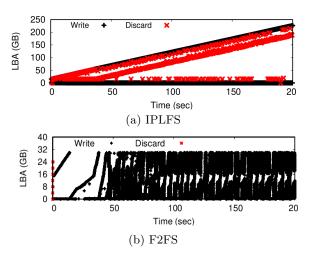

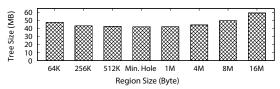

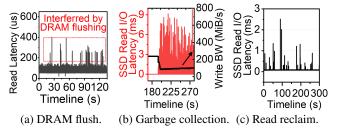

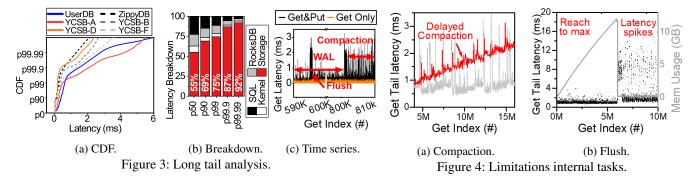

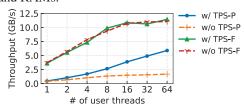

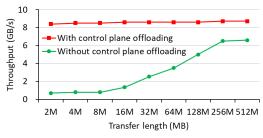

Unfortunately, the broader deployment of SSDs as swap devices is overshadowed by several notable performance issues. One of the key limitations is the system performance degradation as the SSD utilization increases. For example, Figure 1 shows a drastic swap bandwidth drop as the device space usage grows beyond 20%, forcing low space utilization to maintain high performance. In § 3 we thoroughly analyze this and other performance issues with swap on SSDs, such as bandwidth variations for different memory access patterns, and poor isolation in a multi-tenant setting.

These performance anomalies have no simple solution. They stem from the inherent mismatch between the easy-touse block-interface abstraction and the intrinsic flash media

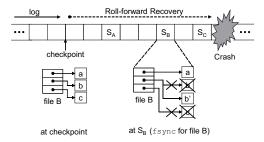

Figure 1: Swap-out bandwidth of random memory accesses (a common swap access pattern [43, 55]), with default Linux swap on Block SSD and ZNSwap on ZNS SSD. The two 1TB SSDs share the same hardware platform and media. WAF—Write Amplification Factor.

properties. In particular, this interface deliberately conceals the absence of in-place updates to flash-based media. Under the hood, updates are written out-of-place to a specifically allocated set of flash blocks (i.e., erase-block). To this end, SSD controllers implement a Flash Translation Layer (FTL), which translates the host-side random writes into sequential writes required by the media, and maintains logic-to-physical mapping for each block. It further entails a device-side Garbage Collection (GC) process to free up erase blocks and reclaim capacity for new writes.

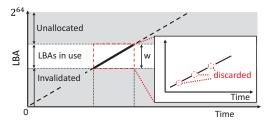

More crucially, this interface decouples the media management from the host-side software stack, so neither the software using the SSD nor the SSD's management logic have any visibility into each other activities. In the context of swap, this decoupling hinders the OS's ability to optimize data placement on the device, and the device's ability to leverage unique characteristics of the swap mechanisms and its usage of the device. For example, the performance degradation observed in Figure 1 is caused by *Write Amplification (WA)*, i.e., the extra data movements performed by the GC. Notably, as we show in § 3, the Write Amplification Factor (WAF) (Figure 1, right) could have been reduced if only the GC were aware of the OS-managed validity status of the stored blocks.

Zoned Storage interface for SSDs (ZNS) [4] aims to reestablish the host's control over key aspects of the storage device management [25]. ZNS opens unique opportunities for crosslayer optimizations that allow novel storage-application codesign simultaneously tailored to the properties of the storage

media and its use by applications [25].

At a high level, ZNS introduces the concepts of zones. Zones disallow in-place updates and require their blocks to be written sequentially. To reclaim the space in a zone it needs to be reset, and new writes can be issued. One important benefit of the ZNS interface over prior attempts to expose flash media control to applications (i.e., raw flash or openchannel SSD [26]), is that it enables host-side storage control without having to deal with low-level media management such as wear-leveling or error correction.

In this work, we introduce **ZNSwap**, a novel swap subsystem for Linux that explores the advantages of the synergy between the SSD management and the OS swap logic, leveraging the ZNS interface to overcome the swap performance issues with block-interface SSDs. While prior works observed that the direct application control over SSDs can be beneficial in the context of file-systems and key-value stores [25, 26, 30, 59], ZNSwap is the first to leverage such control for the OS swap on SSDs.

ZNSwap provides a novel, space-efficient host-side mechanism for SSD space reclamation we call *ZNS Garbage Collector* (ZNGC). Unlike the device-side GC of traditional SSDs, ZNGC is tightly integrated with the OS and has direct access to OS data structures which it uses to optimize its operation.

ZNGC design poses a conceptual challenge, however. The space reclamation process naturally involves the migration of logical blocks on the device, without coordinating the block location changes with the applications that own the stored data. This is not a problem for an SSD-side GC because the user-visible Logical Block Addresses (LBA) remain intact. However, applying this solution to the host-side ZNGC would incur unacceptable space overheads in the host, requiring to maintain reverse mapping for every 4KiB block in TB-scale devices. ZNSwap avoids these overheads in the host by storing the reverse mapping information into the logical block metadata being written alongside the swapped-out page contents. The mapping is guaranteed to be correct during the page lifetime.

More specifically, ZNSwap brings the following benefits: **Fine-grain space management**. ZNSwap obviates the need for TRIM commands, achieving higher performance and better space utilization. The OS uses TRIMs to hint to a Block SSD to deallocate specific LBAs, reducing the load on the SSD-side GC. Unfortunately, the use of TRIMs have been mostly disabled in the OS swap for their large overheads [35, 39, 50, 54], at the expense of significant bandwidth drop due to the artificial space bloat (§ 3.1.1). In ZNSwap, the ZNGC leverages the direct access to the OS internal page validity structures, without the costly overheads associated with TRIMs.

**Dynamic zNGC optimization**. ZNSwap dynamically adjusts the number of swapped-in pages that are also stored in the swap device, improving the performance for read-mostly and mixed read-write workloads. The OS keeps a copy of unmodified swapped-in memory pages in the swap device

to avoid the swap-out penalty for those pages. The amount of disk space such pages may occupy is statically capped by the OS (50% in Linux, non-configurable). However, this static threshold does not fit all workloads: lower values degrade read-mostly workloads, whereas higher values affect mixed read-write workloads (§ 3.1.2). ZNSwap monitors the WAF and decreases the storage occupancy when necessary by reclaiming the SSD space from swapped-in pages.

Flexible data placement and space reclaim policies. ZN-Swap allows easy customization of the disk space management policies to tailor the GC logic to the swap requirements of a specific system. For example, a policy may force colocation of data with similar lifetimes onto the same zone, which was shown to be useful before [28, 34, 44, 56], or achieve better performance isolation by dedicating a separate zone to handle swap from a specific tenant.

Accurate multi-tenancy accounting. As the ZNGC runs on the host, ZNSwap integrates with the cgroup accounting mechanisms to explicitly attribute GC overheads to different tenants, thus improving performance isolation between them.

To summarize, our main contributions are as follows:

- Thorough analysis of traditional Block SSDs' drawbacks when used as swap devices.

- A mechanism to enable ZNS SSDs to serve for swap, without resource-expensive redirection mechanisms in the host, by leveraging logical block metadata for efficient reversemapping.

- Custom swap-aware SSD storage management policies which reduce WA, improve performance, and achieve better isolation in multi-tenant environments.

- Extensive evaluation on standard benchmarks and real applications, demonstrating ZNSwap's performance gains, e.g., up to  $10\times$  lower 99th percentile latency and  $5\times$  higher throughput for memcached, with  $2.5\times$  lower WAF when compared to traditional swap on Block SSD.

#### 2 Background

**OS swap.** When a system encounters memory pressure, it selects victim memory pages for eviction to a *swap device*. The OS unmaps the page chosen for eviction from the pagetables and *swaps-out* the page, writing it to the swap device.

Linux divides the space on a swap device into memory-page-sized blocks called *swap-slots*. The OS allocates a new slot for each page being swapped-out. When a page is swapped-in and the utilized swap device capacity is below 50%, Linux keeps the copy of the page both in memory and in the swap. Such pages belong to the *swap-cache*. The OS evicts swap-cache pages without writing them back to the swap. The swap-slot is freed upon the first write to a swap-cache page, and the page is removed from the swap-cache.

**Block SSD space management.** The SSD's FTL maps Logical Block Addresses (LBAs) to the physical data locations

within erase-blocks on the device. An update to a logical block is implemented by writing the new data to a separate erase-block, and then remapping the host-side LBA to the new block, followed by invalidating the old one. To free space for new writes, a Garbage Collector (GC), executed by the SSD controller, reclaims the invalidated blocks and consolidates the still-valid blocks from multiple erase-blocks to a new erase-block, and then erases the freed erase-blocks. This operation requires over-provisioning (OP) of the flash media in the drive in order to reduce the number of copies during the GC operation.

The device-side GC competes for bandwidth with the user I/O. The relative increase in the amount of data written due to GC vs. the external writes is called a Write Amplification Factor (WAF). The smaller the OP, the higher the WAF and the lower the user-visible performance of the device [34].

Zoned Namespace (ZNS) is a new storage interface for SSDs [25]. A ZNS SSD is organized as a set of logicallyaddressable zones. Each zone is physically aligned to an SSD's erase-block size. Reads inside a zone can be random, but writes must be *sequential*. Writing to a zone can be done via the common write command or through the Zone Append command. The latter works by the host specifying the zone, and the SSD returning the specific write location upon completion, which allows multiple in-flight requests to the same zone [24] (unlike the write command).

Each zone may be either Empty (initial state), Open (after the first write) or Full (no longer writable). The SSD maintains a write pointer to the next logical block for each Open zone. To rewrite a zone, it must be reset, which transitions it into an Empty state. There is a hardware limit on the number of simultaneously Open zones.

#### **Motivation**

Swap performance is important for data centers. The proliferation of fast flash-based storage revitalized the use of swap as a way to maximize memory utilization and reduce costs. Today, swapping does not serve for sustaining severe memory pressure alone. Rather, swap acts as a memory extension during moderate loads, e.g., to optimize the inmemory balance between file-backed and anonymous memory pages [3].

Thus, the swap performance is becoming increasingly important. Recent works propose to accelerate the swap with dedicated hardware [42]. Linux kernel added optimizations to its memory reclamation mechanism [13]. Alibaba Cloud added a per-cgroup background reclaim mechanism [12] to improve multi-tenancy support in data centers. Facebook introduced swap controls for the cgroupv2 mechanism and used it in the fbtax2 project to improve system efficiency [10].

This trend highlights the importance of swap in modern systems. However, most of the current works focused on the OS logic alone. Here we present a thorough analysis of the Linux swap performance focusing on the interplay between the swap logic and the SSD behavior.

#### Performance anomalies of swap on SSDs

#### 3.1.1 GC is not aware of deallocated swap-slots

As shown in Figure 1, the swap bandwidth decreases as the swapped-out data occupies a larger part of the device. In general, this behavior is expected because the GC overheads grow proportionally to the amount of actively updated data. However, the drop should not occur when a device is almost empty (occupied only 10% of its capacity).

The root cause is that the device-side GC is not aware that the OS discards some swapped-out pages and *invalidates* their respective swap-slots because the OS does not by default notify the SSD. Therefore, the actual occupancy of the swap device is much higher than the one visible to the OS, leading to higher GC overheads.

To cope with this issue, most SSDs implement a TRIM command that allows the OS to hint to the SSD to reclaim the storage of invalidated swap-slots. However, in practice, popular Linux distributions (e.g., Debian, Ubuntu) disable the use of TRIM command for swap [7, 9, 15, 21]. The reasons include TRIM dispatching overheads, the long latency of the TRIM command, and the complexity of supporting asynchronous TRIMS [35, 39, 50, 54, 54].

When TRIMs for swap are explicitly enabled, Linux issues the command once for a batch (cluster) of 512 invalidated swap-slots, to reduce the overheads. Notably, these swap-slots must be *contiguous* in the LBA address space [1].

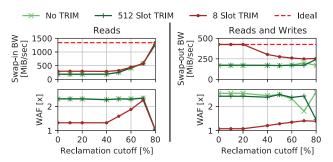

To see the performance effect of TRIMs, we run the same random-write vm-scalability benchmark as in Figure 1, but with TRIMs enabled (see § 6 for the setup). We measure the swap-out bandwidth and WAF over time as the device is being used to illustrate gradual performance degradation.

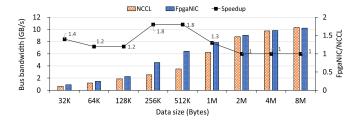

Figure 2 shows that TRIMs (512-slot) have negligible effect. This is because the LBA contiguity requirement of TRIM clusters in Linux effectively prevents issuing TRIMs for the majority of the invalidated slots. These results corroborate the note in the swapon man page [20] that enabling TRIMs often does not improve swap performance.

Finer-grain TRIMs are not effective either. To demonstrate this, we develop a special mechanism that enables TRIMs for small contiguous clusters of eight swap-slots. This is not a practical approach, however, due to its high overheads (see § 6.1.1) Figure 2 shows slight performance improvement, but still 2× lower than the maximum bandwidth. Clusters smaller than 8 slots result in a prohibitively high rate of TRIMs, so the SSD cannot keep up with the swap-slot invalidation rate.

Observation I: TRIMs are not effective at lowering GC overheads for swap.

Figure 2: Swap-out bandwidth over time. Random memory writes using 40% of swap capacity.

Figure 3: Swap-in bandwidth of random reads as a function of swap capacity utilization.

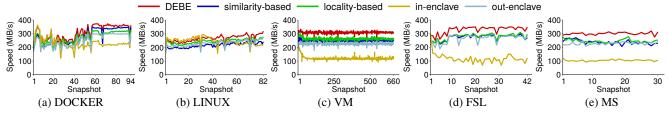

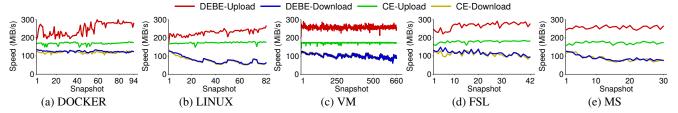

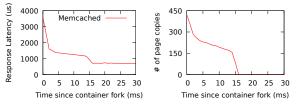

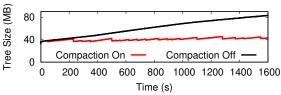

#### 3.1.2 Swap cache is not aware of GC

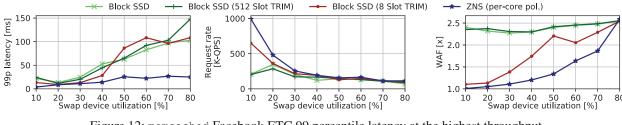

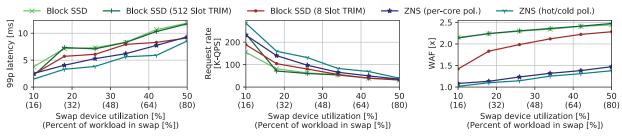

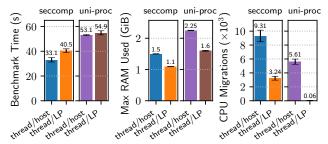

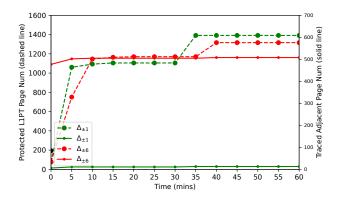

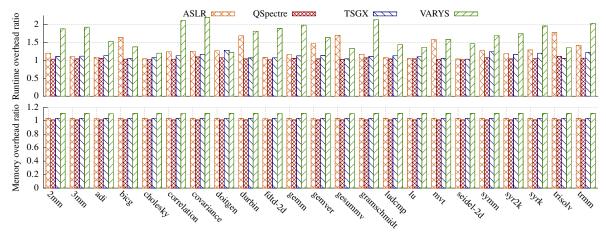

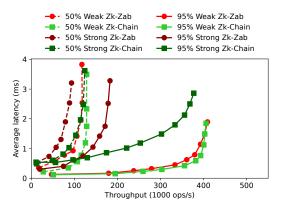

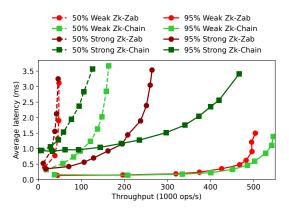

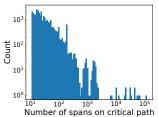

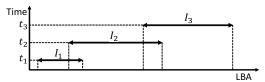

We execute the vm-scalability benchmark to perform uniform random reads on a large chunk of memory exceeding physical RAM and measure the swap performance for different values of the swap device utilization. Ideally, we expect the read performance to be independent of the utilization. Instead, Figure 3 shows a  $6.9\times$  slowdown and  $2.5\times$  WAF above 50% occupancy.

Our analysis shows that this problem occurs due to the way Linux implements its swap-cache. Recall that this cache is comprised of pages that are swapped into memory but the OS still maintains a copy in the swap. When the swap device's utilization exceeds 50% – a hard-coded static parameter we call *swap reclamation cutoff*, Linux stops adding newly swapped-in pages to the swap-cache, invalidating their swapslots immediately. As a result, the swap-out penalty for such pages incurs writing a page to the swap device, rather than discarding them from memory if they were in the swap-cache.

We suggest two possible reasons for this implementation. First, as the swap device gets full, the swap-slot allocation algorithm scans the swap-slot array linearly, which becomes slow [6]. Second, in the context of SSDs, deferring the swap-slot invalidation for in-memory pages effectively increases the device occupancy and eventually reduces performance due to the GC.

Unfortunately, the swap reclamation cutoff establishes a trade-off between the swap-out performance (preferring higher cutoff), and WAF (preferring lower cutoff). To illustrate, we measure the performance of two applications: one performing reads, and the other mixing both reads and writes. This setup aims to show that lower values of the reclamation cutoff are good for write-intensive workloads and bad for read-intensive ones. Higher values mirror this behavior.

We execute vm-scalability configured to use 80% of the swap device's capacity. Half of the working set fits in RAM. Figure 4 shows the swap-in and swap-out bandwidth and WAF as a function of the swap reclamation cutoff. For random reads, the swap-in performance increases with the reclamation

Figure 4: Swap-in and swap-out bandwidth for random reads and mixed reads and writes workloads respectively for different swap reclamation cutoffs.

cutoff, as fewer pages need to be written back upon eviction, with all the pages having copies both in the swap and in memory at the extreme. For the mixed workload, the effect of the cutoff is not visible with the default Linux configuration because the performance is low anyway. But with fine-grain TRIMs and higher baseline performance, smaller cutoff values are preferable.

Observation 2: The static reclamation cutoff strives to strike a balance between read and write performance, but instead aggressively prioritizes write workloads when the swap occupancy grows.

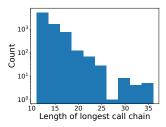

#### 3.1.3 GC is not aware of page access pattern

We evaluate the performance of workloads with different memory access patterns using pmbench. We consider two write workloads: with uniform and with skewed access distributions (normal,  $\sigma = \frac{1}{12}$  of the working set size, the default in pmbench). The swap-out bandwidth is 480MiB/sec (maximum for this SSD), and 195MiB/sec (WAF is 2.5) respectively, when using 5% of the swap capacity and 512-slot TRIMs enabled.

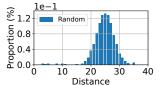

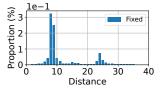

This difference stems from the different lifetimes of swapped-out pages. With the skewed distribution of memory writes, there are fewer opportunities for the swap subsystem to find large contiguous clusters of swap-slots to perform TRIMS, whereas uniformly distributed writes result in the swap-slots of similar lifetimes, increasing the chances of finding such clusters. 8-slot TRIMS are better, but the performance is still suboptimal: 324MiB/sec, with WAF of 1.5×.

Observation 3: Swap performance may vary significantly depending on the memory access pattern.

#### 3.1.4 GC is not aware of OS's performance isolation

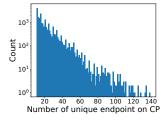

Linux's cgroup mechanism enforces resource isolation among different processes. In particular, it is possible to isolate swap bandwidth via blk-throttle. This is useful, e.g., in container-based virtualized environments to prevent performance interference between containers.

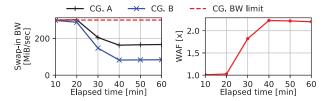

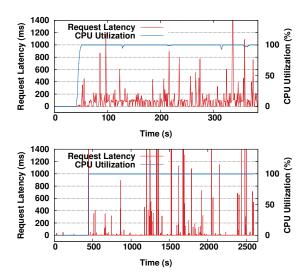

Figure 5: Swap-in bandwidth and WAF of 100%-random-read cgroup (A) and 50/50%-random-read/write cgroup (B) co-running together, each throttled to 300MiB/sec reads and 300MiB/sec writes.

We now evaluate the quality of the performance isolation in a scenario where we expect no interference. We run two processes, each in its own cgroup limited to 300MiB/sec reads and 300MiB/sec writes from/to the swap device. One process performs 100% reads and the other executes an equal mix of reads and writes, all uniformly distributed. To prevent any interference the processes are pinned to separate sets of cores, each with its own device queue. The aggregate bandwidth of the SSD does not reach its limit (1GiB/sec).

We expect both processes to achieve their maximum bandwidth allocation. In practice, during the first 20min of the execution (Figure 5) no GC is performed, thus the SSD sustains the cumulative request rate from both processes. When the GC is triggered, the swap-in bandwidth of *both* cgroups drops. Importantly, the first process performs only reads, and should not have been affected by the GC overheads caused only by the writes of the second process. This behavior stems from the GC's inability to distinguish between the I/Os from different processes, and the OS's inability to enforce bandwidth limits on the GC.

Observation 4: The GC impairs performance isolation dictated by the host OS.

#### 3.2 Opportunities with swap on ZNS

ZNS SSDs provide better control over physical data placement, thereby enabling tighter coupling between the application logic and the device management, and have already been shown to offer new optimization opportunities for production Key-Value-Stores [25]. These results motivate a new GC-swap subsystem co-design that can leverage this coupling to mitigate the performance problems of traditional SSDs discussed above.

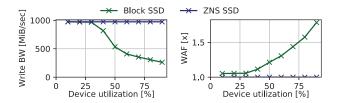

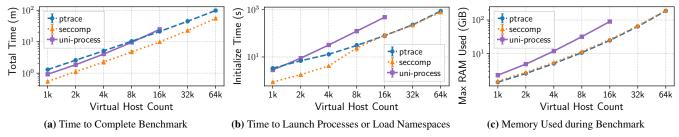

**Is ZNS essential for performance?** An important question is whether there is an inherent benefit to using ZNS SSDs over traditional ones, or one can redesign the swap subsystem alone to achieve the same outcome. In other words, can we achieve the performance of ZNS by emulating it on top of a Block SSD?

To answer, we run an experiment on a Block SSD while using a write access pattern that mimics the one enforced by ZNS zones. We run multiple threads, each performing

Figure 6: Write bandwidth and WA of sequential writes and TRIM operations to erase-block sized regions on Block SSD and ZNS SSD as a function of device utilization.

4KiB logically sequential writes with 1GiB-TRIMs (the size of an erase-block and a ZNS zone on our device). Each thread accesses its own part of a drive, and overwrites the available space, issuing a TRIM for the whole next 1GiB chunk. Multiple threads are used to emulate typical swap behavior.

We run the experiment for different values of device utilization. Figure 6 shows the results. We observe that the performance starts to decrease when a device is 30% full, drops to a half of the maximum bandwidth at 50%, and degrades down to a quarter at 80%. This is expected because the Block SSD cannot ensure that host-side TRIMs are aligned with physical erase-blocks as the writes from different threads get mixed in the device, even though the host strives to align them at the LBA level. In contrast, the same experiment on ZNS drives maintains full bandwidth no matter how full the device is.

We conclude that the ZNS interface offers unique advantages that cannot be achieved with traditional Block SSDs.

**ZNS adoption.** ZNS SSDs are expected to gain broader adoption in the near future. They hold the promise to reduce storage costs as they lower the internal DRAM size requirements, and might help reduce media overprovisioning via application-optimized software stack [25].

While the ZNS interface is not backward compatible with the in-place block interface, there is growing support for ZNS at the file system level. For example, F2FS and Btrfs in Linux can utilize ZNS drives.

These trends motivate us to tailor OS swap for ZNS SSDs.

#### 4 Design

ZNSwap addresses three key design goals.

Resource-efficient Host-side GC. Reclaiming storage space in ZNS SSDs requires a host-side process akin to a GC that consolidates valid blocks from fragmented zones into new ones, subsequently erasing the freed zones. The primary challenge is in minimizing the memory and CPU overheads associated with the host-GC operation. This is because, unlike the device-side GC, the host-side GC directly competes for these host resources with regular applications. In essence, we need to *on-load* the GC onto the CPU from the device with minimal costs, thereby enabling its tighter integration with the swap.

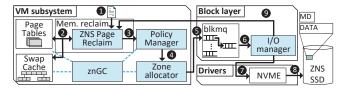

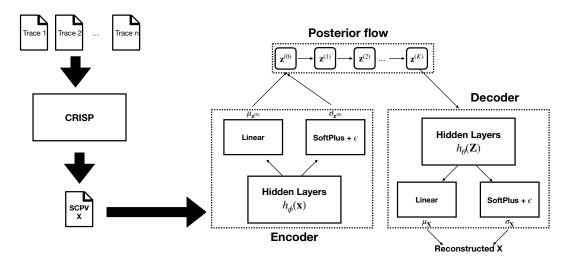

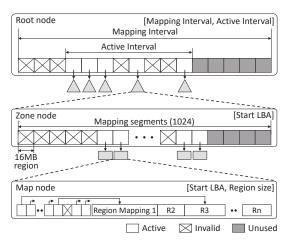

Figure 7: ZNSwap overview. Shaded shapes are internal ZN-Swap components.

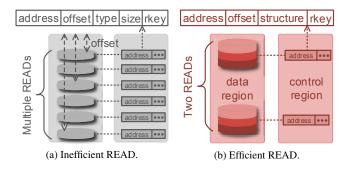

These resource constraints preclude direct porting of existing host-side GC implementations. In particular, such implementations commonly maintain large translation tables (FTL) [32, 37], which consume about 1GiB for every TiB of data. The tables are frequently updated by writes and GC operations and accessed during reads. Given the typically poor locality of swap-induced I/O accesses [43, 55], these tables have to be resident in host memory. Maintaining the extra level of indirection between logical and physical block addresses appears to be inevitable to allow the host-side GC to move data without affecting the applications using it.

Our host-side GC, znGC, eliminates the need for the extra level of indirection entirely. It takes advantage of the fact that the swapped-out pages are still maintained in their owner's page tables, and thus stores the relevant kernel reverse mapping metadata alongside the swapped-out page in the SSD. It also avoids I/O overheads to manage the reverse mappings by using the per-LBA metadata region available in NVMe devices as we describe in §§ 4.2 and 5.1.

**ZNGC-OS integration.** The key benefit of ZNGC over device-side GC is the ability to access the information exposed by the OS to optimize the swap I/O performance. For example, ZNGC may consult the OS-maintained swap-slot array to identify OS-invalidated swap-slots and avoid redundant copies without using TRIMs. We explain this and additional optimizations in § 4.3.

**Swap data placement policies.** Swap data placement may have a significant effect on the system performance, but the placement policy may depend on the specific execution environment. For example, a policy to achieve better resource isolation between a pair of processes might prefer storing all the pages of the same process in the same SSD zone. We strive to facilitate the implementation of such policies via a set of APIs that hide the complexity of zone management and ZNGC logic. We explain the API and the policies in § 4.3.

#### 4.1 Overview

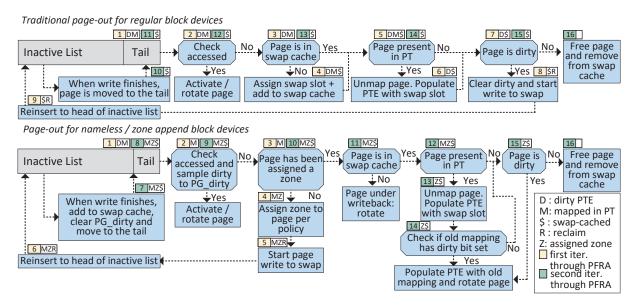

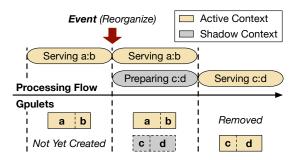

Figure 7 shows ZNSwap's main design components. We explain each component and its role using the swap-out path as an example.

After a page to be swapped-out is selected by the OS, it is passed to the *ZNS page reclaim* • which handles the pagetable and swap-cache operations • In contrast to the original swap logic, it updates the destination location for the swapped-

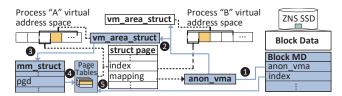

Figure 8: Linux reverse mapping overview. Shaded shapes are data structures accessed during ZNGC reverse mapping.

out page *after* it has been written, as dictated by the ZNS zone-append interface. Before writing a page, the page reclaim module consults the *policy manager* 3 which determines the destination *zone* and may guide ZNGC to free certain zones on the device. The policy manager incorporates custom policies that can be tailored to specific system requirements. The *zone allocator* 4 seamlessly handles Full zones and allocates a new zone when necessary.

The page is then submitted to the block layer (a), which subsequently passes the page to ZNSwap's *I/O manager* (b). The I/O manager merges zone-append operations whenever possible, and generates an I/O request containing the page's data and reverse mapping information used by ZNGC. Finally, the I/O manager hands off the I/O requests to the NVMe driver (a) which writes to the ZNS SSD (a), and updates the reclaim module with the page location on the SSD (a).

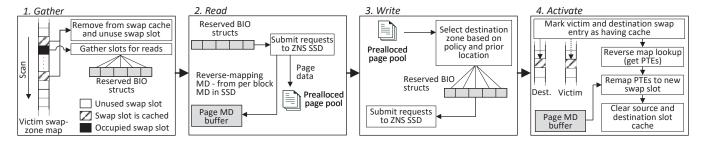

#### 4.2 ZNGC

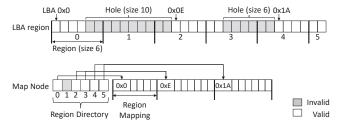

ZNSwap's reclamation mechanism, ZNGC, is tightly integrated with the kernel virtual memory (VM) subsystem. ZNGC runs as a daemon in the kernel and is triggered either when the number of Empty zones is low, or via explicit requests by the ZNSwap policy.

Contrary to Block SSDs, a page moved by ZNGC is assigned a new host-visible address. Without an additional translation layer, ZNGC must update the page tables holding the original page swap-slot to reflect the new location. To this end, ZNGC stores the relevant reverse-mapping metadata along-side the data in the ZNS SSD's per-LBA metadata region to assist later in updating the page tables. The storage interface (i.e., NVMe) allows to retrieve the metadata together with the respective data block in a single I/O operation. Thus, ZNGC retrieves the metadata to perform the reverse lookup of a given page and then updates the page table(s) that own it.

An important question remains: *which information* needs to be stored in the page metadata to guarantee that the reverse mapping remains correct during its lifetime?

To answer it, we leverage the same main data structures and procedures in the Linux kernel used to implement its reverse mapping scheme (Figure 8).

**Background: Linux memory mapping structures.** Recall that virtual memory pages in a process' address space belong to virtual memory areas (vmas) that represent virtual memory allocations. vmas belong to a processes' virtual memory

address spaces (mm structs), which hold the page table directory (pgd). The physical page descriptor (struct page) holds metadata enabling the reverse mapping. ZNGC stores the same metadata fields in the logical block's metadata on the SSD.

To locate all page table entries associated with a physical page, the reverse mapping procedure accesses the anon\_vma 1 data structure, which is present between each physical page and the virtual memory area (vma) structures that map it<sup>1</sup>. The anon\_vma structure holds a list of vmas which may map the page 2 and accounts for changes to the virtual mappings of the physical page. The physical page's descriptor (struct page) does not not directly account virtual mapping changes, rather, the descriptor holds a pointer to the anon vma in its mapping field.

The mm\_structs of each of the vmas that may map the page are accessed 3, and their page tables are walked 4 to locate the page table entries. To calculate the virtual address used to walk the page tables, the index metadata value 6 along with the vma's start virtual memory address are used. The physical address corresponding to the physical page we have initialized the reverse mapping procedure is located in the last level page table entries and subsequently returned. Since swapped-out pages do not have a valid physical address in their page table entry, ZNGC returns the entries that hold the swapped-out location of the swap-slot we were performing the reverse mapping procedure.

Since the anon vma structure is freed when there are no more vmas which may map the page and the anon\_vma pointer in the struct page does not change, storing the pointer to the anon\_vma as well as the mapping's offset (index) within the logical block's metadata on the SSD enables the same functionality as reverse mapping within the kernel.

#### 4.3 **ZNGC-swap integration**

**Physical zone information.** Each zone is associated with a map of swap-slots. The map holds information on the use of each swap-slot, and whether it is valid, or swap-cached (similar to Linux's swap map). This information is used by ZNGC during the space reclamation. Note that a swap-slot can be discarded by the OS and ZNGC becomes immediately aware of the change, without using TRIMs as in Block SSDs. ZNGC may decide to reclaim some zones that are mostly free but hold some of the swap cache pages if it runs out of free storage space, making the swap reclamation cutoff parameter in Linux unnecessary.

Swap-zone abstraction. Active zones that can be used for swap-slot allocation are exposed via a swap-zone abstraction. A swap-zone is a virtual entity used to hide the complexity of managing physical SSD zones. Swap-zones are backed by Open zones. When an underlying physical zone transitions

| Function                                                                                                                                                                                                                                                                    | Purpose                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| void rec_zn(int zn)                                                                                                                                                                                                                                                         | Reclaim specified zone                                                                                                                                                                                                                             |

| <pre>void pg_inf(pg_i*, u64 pfn) void vm_inf(vm_i*, u64 pfn) void zn_inf(zn_i*, int zn) void swap_inf(swap_i*)</pre>                                                                                                                                                        | Get page statistics<br>Get information on VMA<br>Get information on zone<br>Get ZNSwap statistics                                                                                                                                                  |

| <pre>typedef struct {    u64 last_swapout_t;    u16 access_bit_vec;    int owner_pid;    u64 cgroup_id; } pg_i;  typedef struct {    int zone_id;    int capacity;    int occupied_slots;    int invalid_slots;    int swap_cache_slots;    int swap_zone_id; } zn_i;</pre> | <pre>typedef struct {   u64 vm_flags;   u64 size;   int readahead_win_sz;   u64 cgroup_id; } vm_i; typedef struct {   u64 num_{slots,zns};   u64 free_{slots,zns};   u8 zslot_array_sz;   u32 {high,low}_wmark;   bool gc_running; } swap_i;</pre> |

Table 1: ZNGC policy API.

to the Full state, it is seamlessly replaced by another Open physical zone. The total number of swap-zones is determined by the limit on the number of Open zones in the device.

**ZNSwap policies.** ZNSwap provides an API to facilitate the development of custom data placement and zone reclamation policies. A policy is invoked when the OS swaps-out a page, and its primary goal is to determine which swap-zone the page is written to. If there is a need to reclaim some of the zones, the policy may (asynchronously) invoke ZNGC to do so for a specific set of zones. The policies are implemented in a kernel module. Note that the swap-slot allocation policy operates at the granularity of swap-zones rather than swap-slots to conform to the ZNS interface.

**API.** A policy receives the page frame number (pfn) of the page being swapped-out and returns the swap\_zone\_id of the swap-zone where the swap-slot should be allocated. Table 1 lists the functions that can be invoked by the policy.

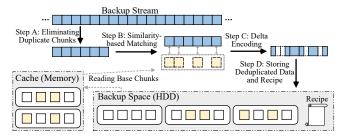

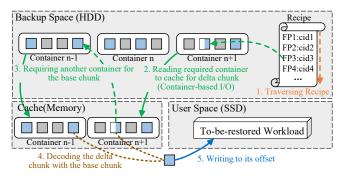

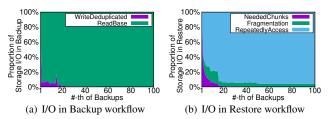

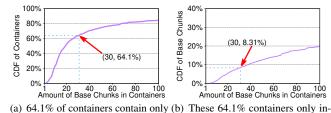

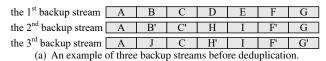

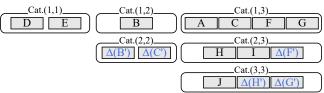

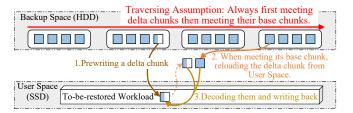

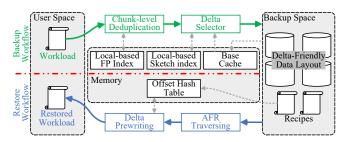

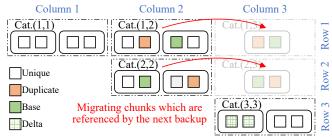

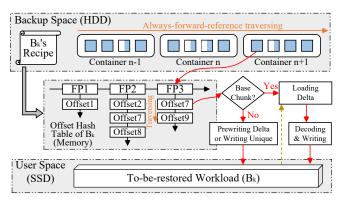

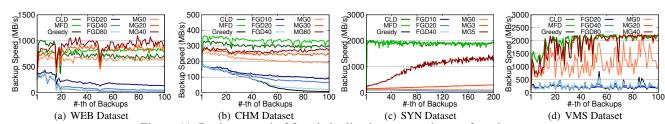

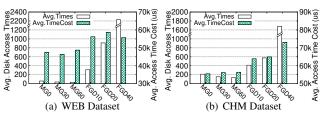

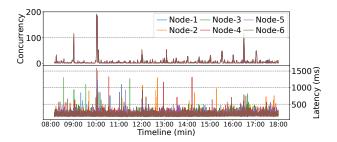

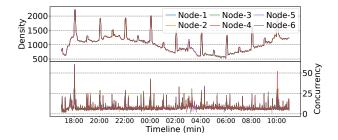

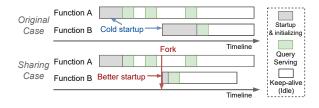

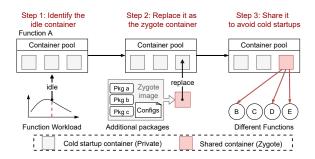

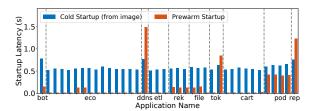

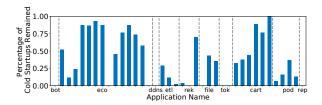

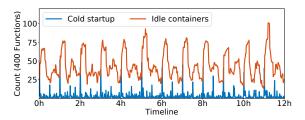

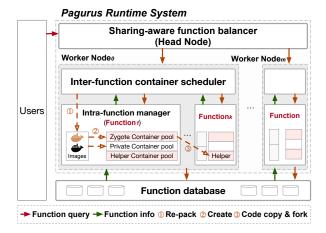

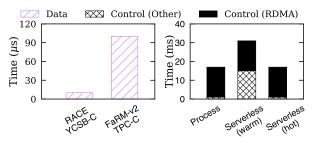

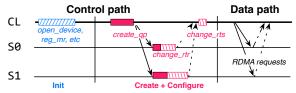

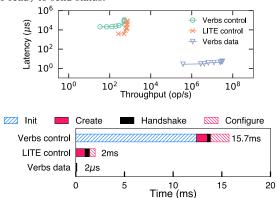

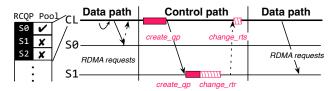

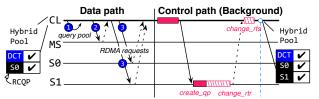

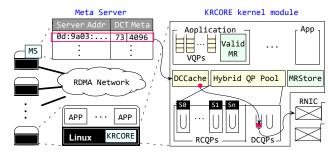

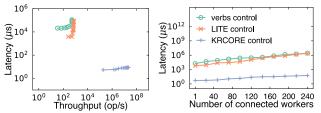

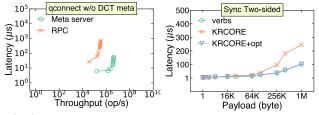

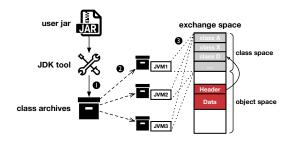

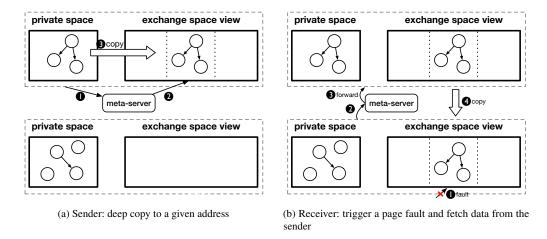

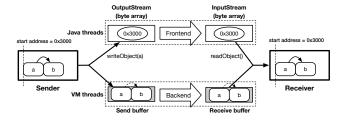

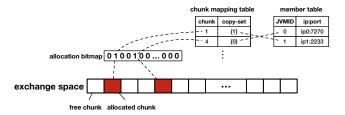

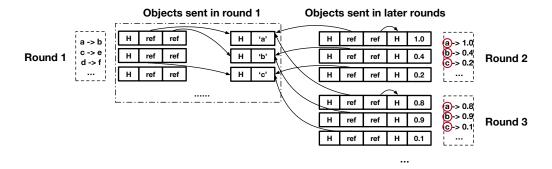

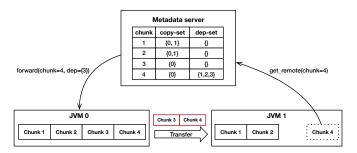

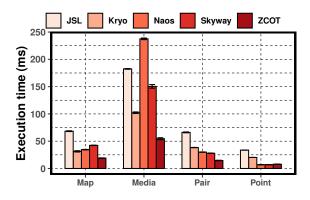

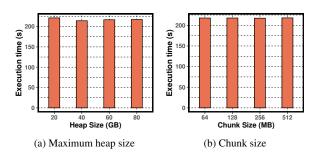

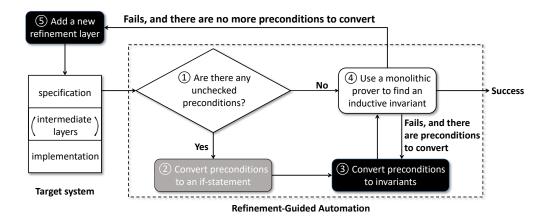

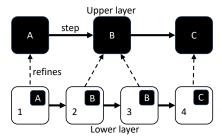

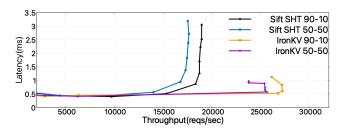

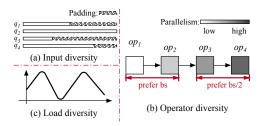

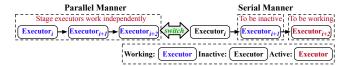

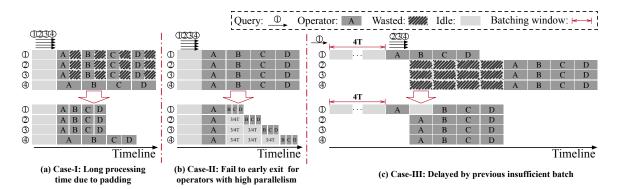

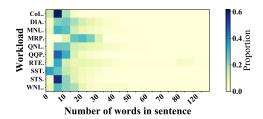

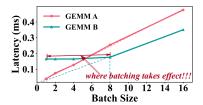

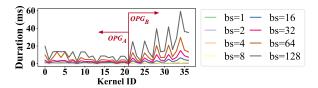

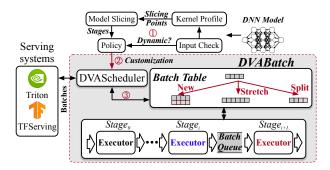

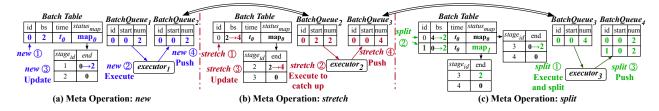

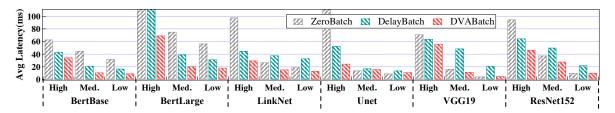

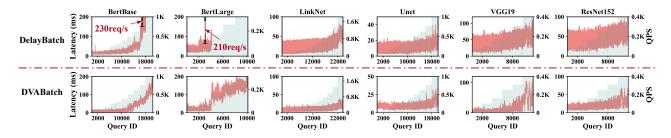

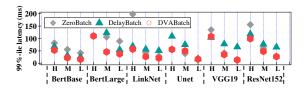

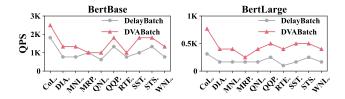

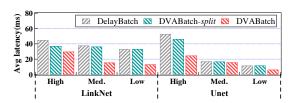

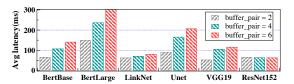

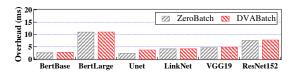

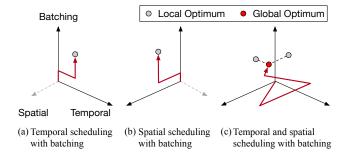

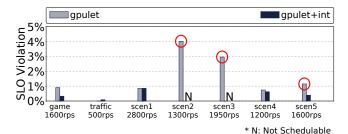

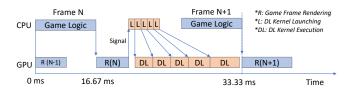

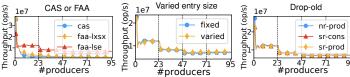

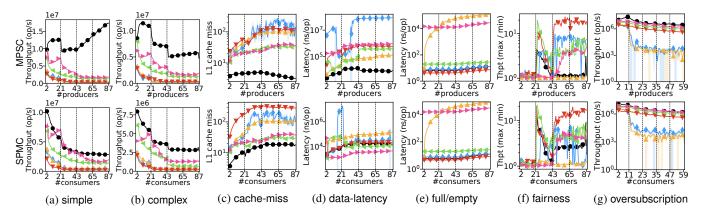

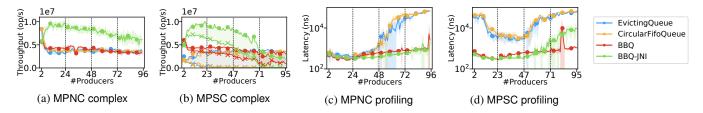

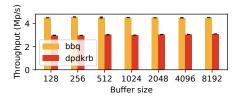

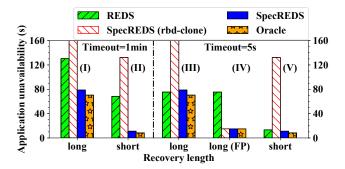

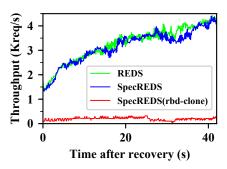

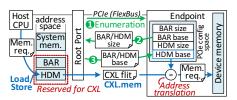

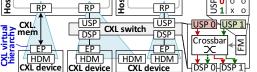

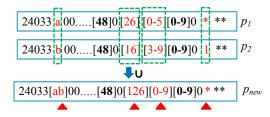

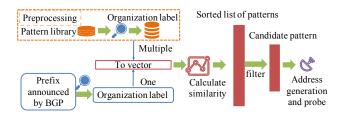

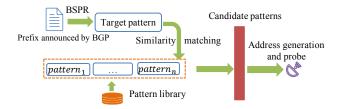

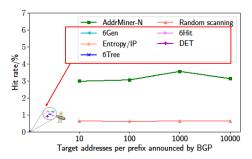

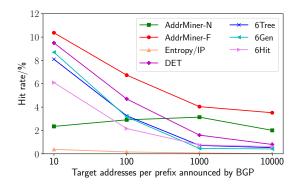

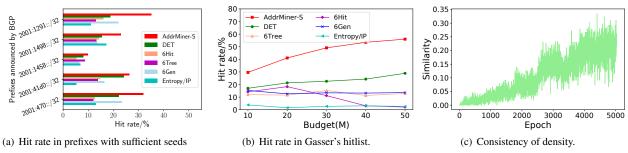

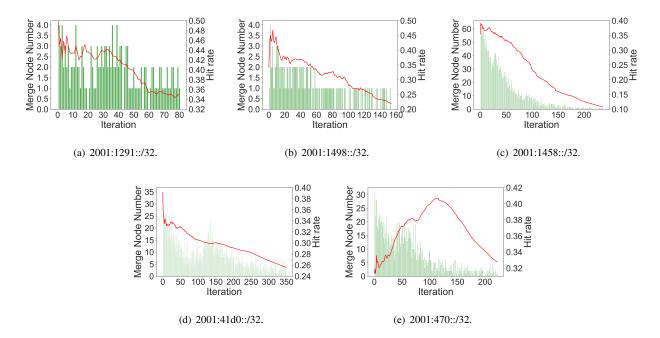

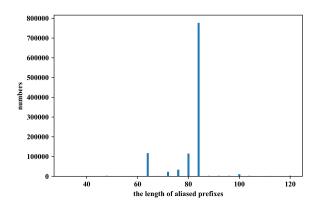

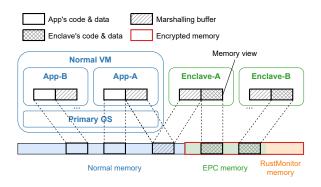

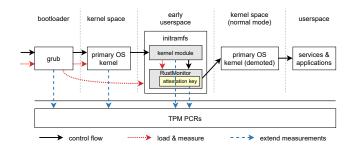

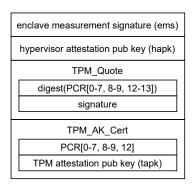

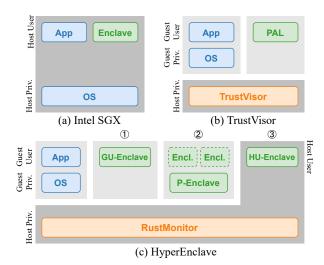

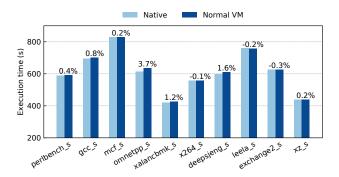

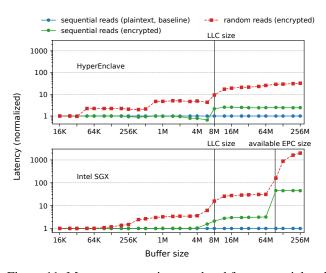

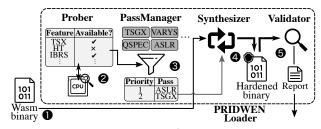

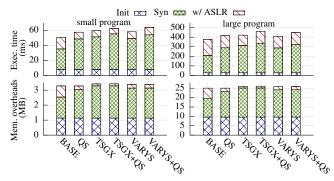

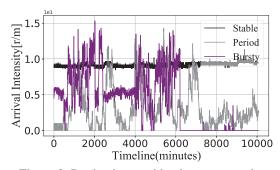

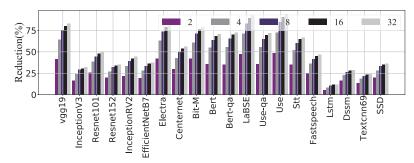

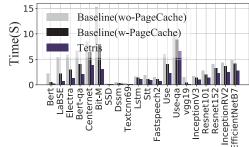

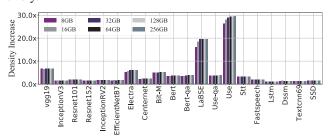

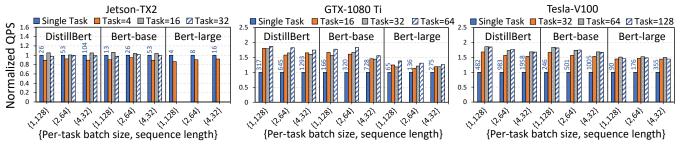

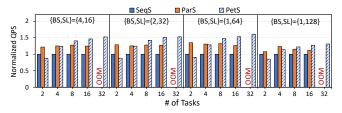

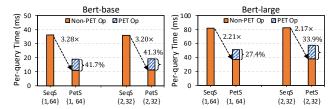

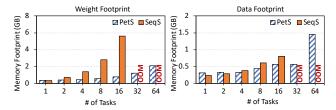

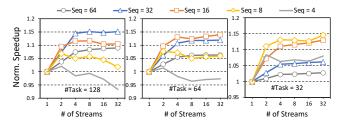

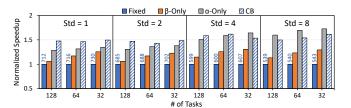

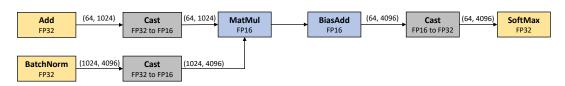

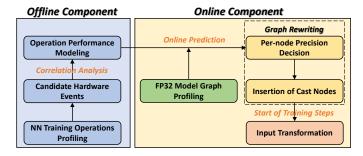

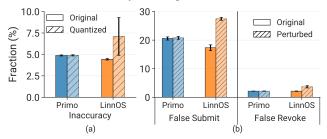

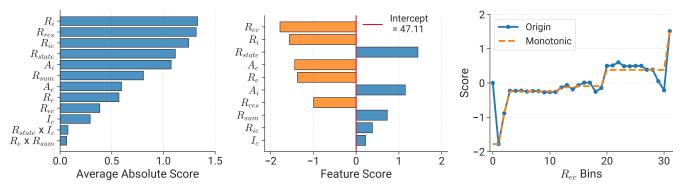

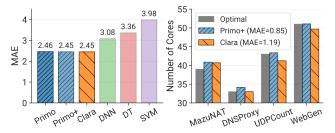

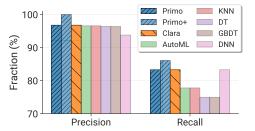

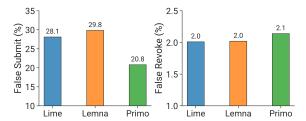

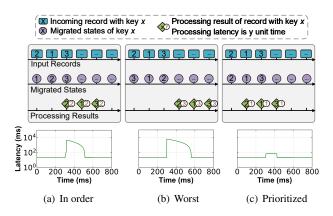

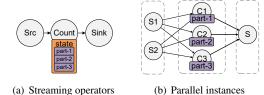

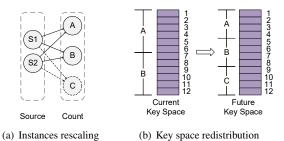

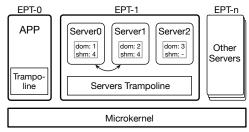

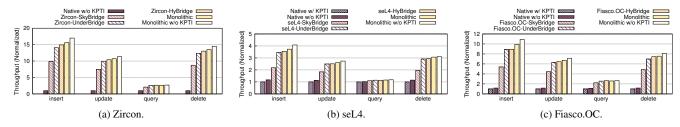

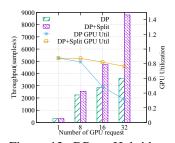

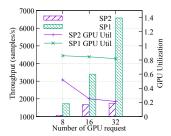

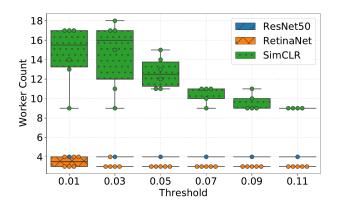

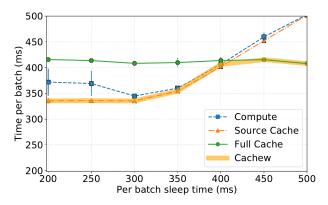

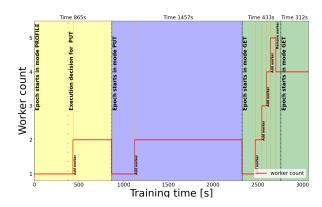

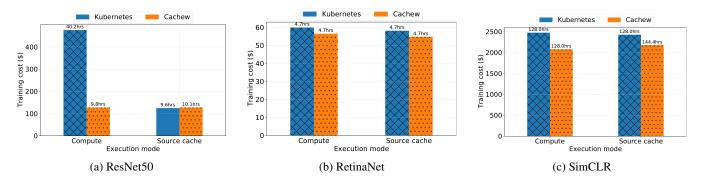

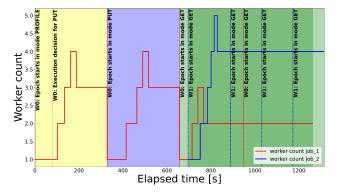

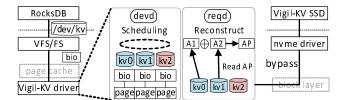

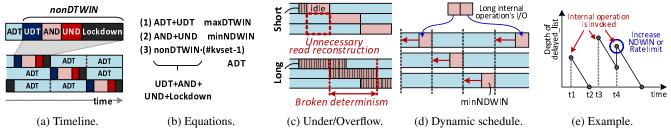

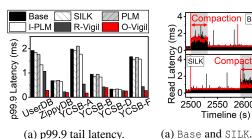

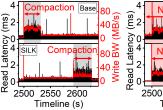

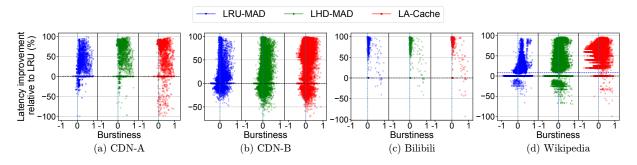

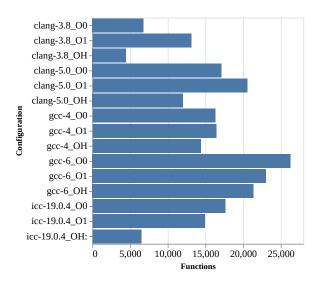

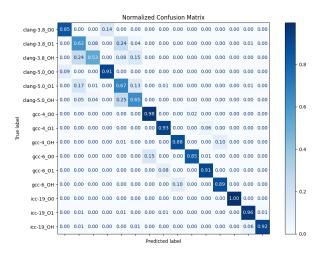

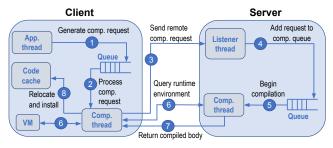

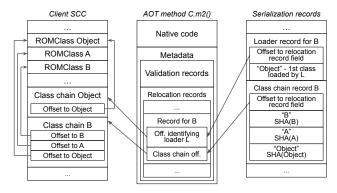

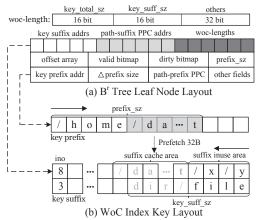

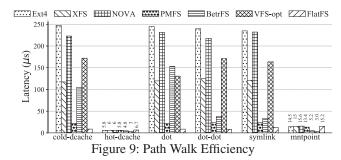

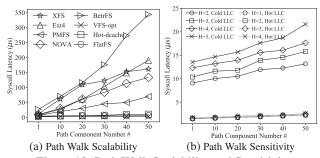

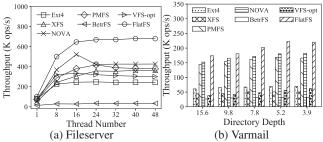

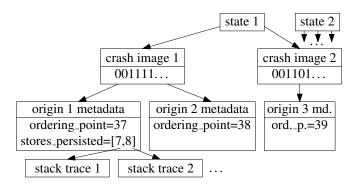

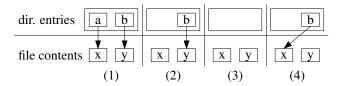

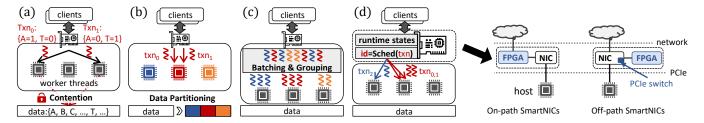

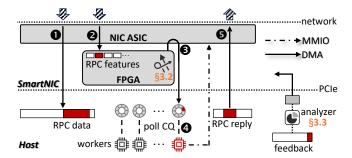

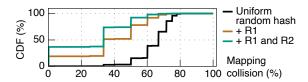

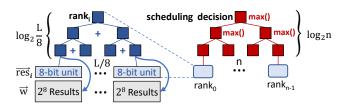

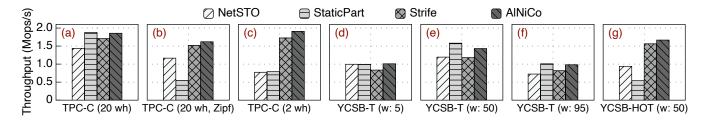

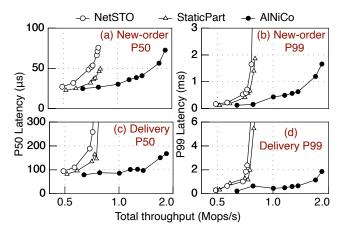

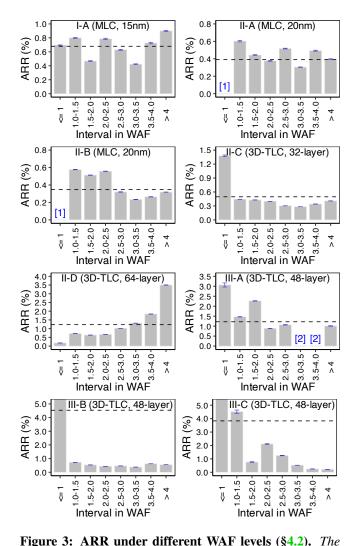

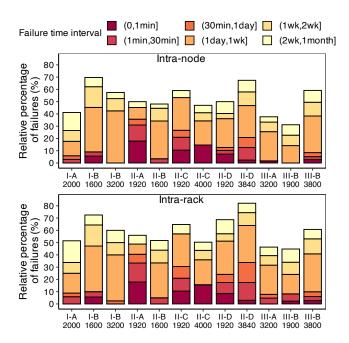

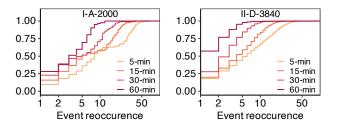

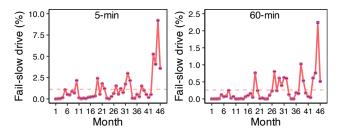

We define three sample policies: